## Wireless Components

ASK/FSK Transmitter 868/433 MHz TDA 5100

Application Note Version 1.2, March 2000

| <b>Revision Hist</b>             | tory                                  |                                              |  |  |

|----------------------------------|---------------------------------------|----------------------------------------------|--|--|

| Current Versio                   | Current Version: 1.2 as of 09.03.00   |                                              |  |  |

| Previous Vers                    | Previous Version: 1.1, September 1999 |                                              |  |  |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version)       | Subjects (major changes since last revision) |  |  |

|                                  |                                       |                                              |  |  |

|                                  |                                       |                                              |  |  |

ABM®, AOP®, ARCOFI®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE<sup>™</sup>, ASM<sup>™</sup>, ASP<sup>™</sup>, POTSWIRE<sup>™</sup>, QuadFALC<sup>™</sup>, SCOUT<sup>™</sup> are trademarks of Infineon Technologies AG.

Edition 06.03.00 Published by Infineon Technologies AG, Balanstraße 73, 81541 München

© Infineon Technologies AG March 2000. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you - get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

# **1** Table of Contents

| 1   | Table of Contents                         |

|-----|-------------------------------------------|

| 2   | Product Description                       |

| 2.1 | Abstract                                  |

| 2.2 | Overview                                  |

| 2.3 | Package Outlines                          |

| 3   | Functional Description                    |

| 3.1 | Pin Configuration                         |

| 3.2 | Pin Definitons and Functions              |

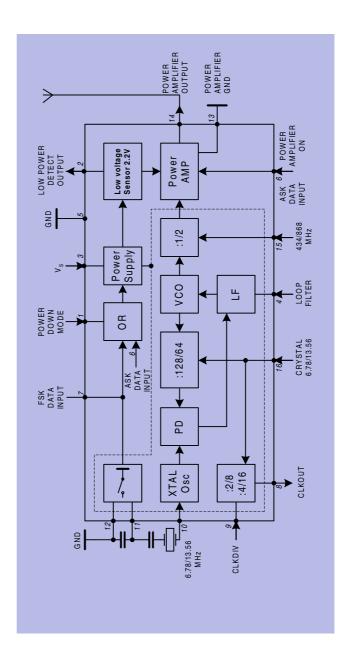

| 3.3 | Functional Block Diagram                  |

| 4   | Applications                              |

| 4.1 | Antenna                                   |

| 4.2 | Reference Oscillator                      |

| 4.3 | Frequency stability4-13                   |

| 4.4 | Modulation                                |

| 4.5 | Lock time                                 |

| 4.6 | Clock output                              |

| 5   | Reference                                 |

| 5.1 | Application Circuit                       |

| 5.2 | Test Board Layouts5-3                     |

| 5.3 | Bill of material (Application Circuit)5-4 |

| 5.4 | Application Board                         |

**Table of Contents**

#### **Contents of this Chapter**

| 2.1 | Abstract         | . 2-2 |

|-----|------------------|-------|

| 2.2 | Overview         | . 2-3 |

| 2.3 | Package Outlines | . 2-4 |

#### **Product Description**

### 2.1 Abstract

This application note describes the operation of the TDA5100 evaluation board. It demonstrates the design of a low-cost transmitter for applications in wireless I.S.M. data communication systems. A variety of application considerations are provided to assist system designers in implementing the device as a low-cost data transmitter.

The circuit board can be operated in all the modes supported by the TDA5100:

- in one of the assigned frequency bands for Short Range Devices (SRD) at either 434MHz or 869MHz

- using amplitude shift key (ASK) or frequency shift key (FSK) modulation.

The board conforms to the I-ETS 300 220 regulations.

#### **Product Description**

#### 2.2 Overview

The TDA 5100 has been implemented in a 25GHz silicon bipolar process (Siemens process "B6HF"). It supports all low power device (LPD) wireless applications with data rates of up to 100kb/s using ASK- and up to 40kb/s using FSK-digital modulation.

The basic configuration is a PLL frequency synthesizer circuit with an on-chip fully integrated VCO operating at a frequency in the 869MHz range. This frequency is divided by 64 for operation at a reference frequency of 13.5MHz or by 128 at a reference frequency of 6.8MHz.

The power amplifier is driven by the VCO with an isolation driver stage for operation at 869MHz. Operation at 434MHz is achieved by first dividing the VCO frequency by two. The power amplifier is a class C configuration. It has been optimized for high power efficiency.

Modulation is achieved by either modulating the frequency of the reference oscillator in FSK applications or by modulating the carrier amplitude using a digital output power control pin in ASK applications.

Table 2-1 summarizes the key parameters of the device:

| ParameterSelectable frequency range 433-435 MHz and 868-870 MHzFully integrated VCO and PLL synthesizerHigh efficiency power amplifierOutput power +4dBm (434MHz), +1dBm (869MHz)Supply voltage range 2.1 V - 4.0 VLow supply current I <sub>S</sub> =6.9mA typ.ASK / FSK modulationPower down modeLow-voltage detect functionClock output for controller | Table 2-1 Performance Summary for the TDA5100 Transmitter |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Fully integrated VCO and PLL synthesizer   High efficiency power amplifier   Output power +4dBm (434MHz), +1dBm (869MHz)   Supply voltage range 2.1 V - 4.0 V   Low supply current I <sub>S</sub> =6.9mA typ.   ASK / FSK modulation   Power down mode   Low-voltage detect function   Clock output for controller                                        | Parameter                                                 |

| High efficiency power amplifier   Output power +4dBm (434MHz), +1dBm (869MHz)   Supply voltage range 2.1 V - 4.0 V   Low supply current I <sub>S</sub> =6.9mA typ.   ASK / FSK modulation   Power down mode   Low-voltage detect function   Clock output for controller                                                                                   | Selectable frequency range 433-435 MHz and 868-870 MHz    |

| Output power +4dBm (434MHz), +1dBm (869MHz)   Supply voltage range 2.1 V - 4.0 V   Low supply current I <sub>S</sub> =6.9mA typ.   ASK / FSK modulation   Power down mode   Low-voltage detect function   Clock output for controller                                                                                                                     | Fully integrated VCO and PLL synthesizer                  |

| Supply voltage range 2.1 V - 4.0 V<br>Low supply current I <sub>S</sub> =6.9mA typ.<br>ASK / FSK modulation<br>Power down mode<br>Low-voltage detect function<br>Clock output for controller                                                                                                                                                              | High efficiency power amplifier                           |

| Low supply current I <sub>S</sub> =6.9mA typ.<br>ASK / FSK modulation<br>Power down mode<br>Low-voltage detect function<br>Clock output for controller                                                                                                                                                                                                    | Output power +4dBm (434MHz), +1dBm (869MHz)               |

| ASK / FSK modulation<br>Power down mode<br>Low-voltage detect function<br>Clock output for controller                                                                                                                                                                                                                                                     | Supply voltage range 2.1 V - 4.0 V                        |

| Power down mode<br>Low-voltage detect function<br>Clock output for controller                                                                                                                                                                                                                                                                             | Low supply current I <sub>S</sub> =6.9mA typ.             |

| Low-voltage detect function<br>Clock output for controller                                                                                                                                                                                                                                                                                                | ASK / FSK modulation                                      |

| Clock output for controller                                                                                                                                                                                                                                                                                                                               | Power down mode                                           |

|                                                                                                                                                                                                                                                                                                                                                           | Low-voltage detect function                               |

|                                                                                                                                                                                                                                                                                                                                                           | Clock output for controller                               |

| Fast lock up time ≤1ms                                                                                                                                                                                                                                                                                                                                    | Fast lock up time ≤1ms                                    |

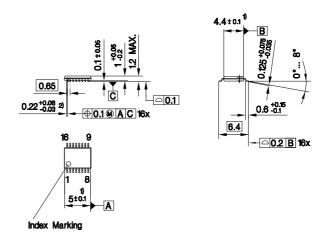

## 2.3 Package Outlines

P-TSSOP-16

1) Does not include plastic or metal protrusion of 0.15 max. per side 2) Does not include dambar protrusion

#### **Contents of this Chapter**

| 3.1 | Pin Configuration            | . 3-2 |

|-----|------------------------------|-------|

| 3.2 | Pin Definitons and Functions | . 3-3 |

| 3.3 | Functional Block Diagram     | . 3-7 |

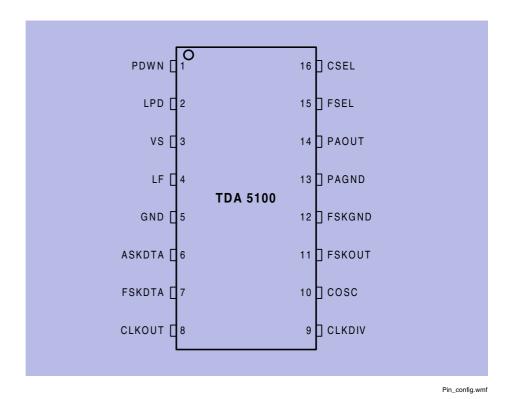

## 3.1 Pin Configuration

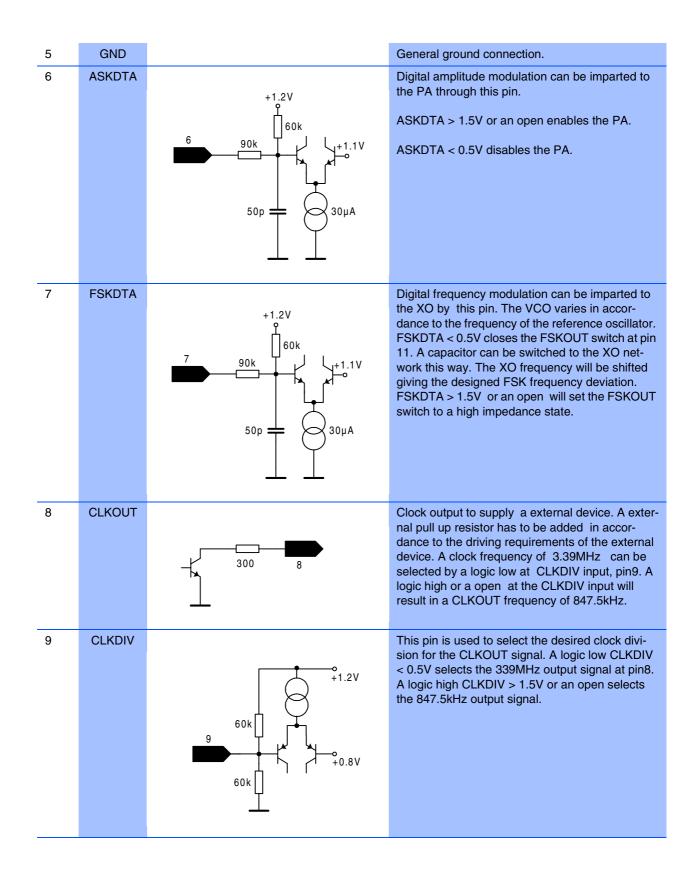

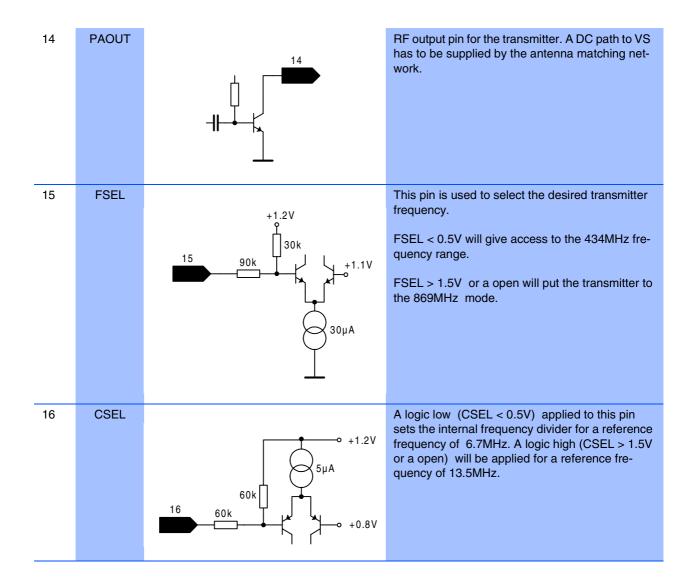

## 3.2 Pin Definitons and Functions

| Table      | 3-1    |                                                        |                                                                                                                                                                                                                                                                          |

|------------|--------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>No. | Symbol | Interface Schematic                                    | Function                                                                                                                                                                                                                                                                 |

| 1          | PDWN   | ASKDTA<br>FSKDTA<br>UVS<br>150k<br>150k<br>250k<br>UN" | Disable pin for transmitter circuit.<br>PDWN < 0.7V turns off all transmitter functions.<br>PDWN > 1.5V gives access to all transmitter<br>functions.<br>PDWN input will be pulled up by 40µA internally<br>by either setting FSKDTA or ASKDTA to a logic<br>high state. |

| 2          | LPD    | 40μA<br>300 2                                          | This pin provides an output indicating the low-<br>voltage state of the supply voltage VS.<br>VS < $2.15V$ will set LPD to the low state.<br>An internal pull up current of $40\mu$ A gives the out-<br>put an high state at supply voltages above<br>2.15 V.            |

| 3          | VS     |                                                        | This pin is used to supply DC bias to the transmit-<br>ter electronics. A RF bypass capacitor should be<br>connected directly to this pin and returned to<br>ground as short as possible.                                                                                |

| 4          | LF     | $v_s$<br>15p<br>35k<br>10k<br>4                        | Output of the charge pump and input to the VCO control. An internal loop filter has been designed for a loop bandwidth of 150kHz. The loop bandwidth may be reduced by applying an external RC network.                                                                  |

Infineon

| 10 | COSC   |                                       | This pin is connected to the reference oscillator<br>circuit. The reference oscillator configuration is of<br>the negative impedance converter type. It pre-<br>sents a negative resistor in series to an inductor<br>at the COSC pin.                                                                                                                                                                                         |

|----|--------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | FSKOUT | V <sub>s</sub><br>200µA<br>1,5k<br>11 | This pin is a switch being activated by the<br>FSKDTA signal at pin 7. The switch is closed for<br>a logic low at the FSKDTA pin. It is open for a<br>logic high or a open at the FSKDTA input. FSK-<br>OUT will switch an additional capacitor to the ref-<br>erence crystal network to pull the crystal<br>frequency by an amount resulting in the designed<br>FSK frequency shift of the transmitter output fre-<br>quency. |

| 12 | FSKGND |                                       | Ground connection for FSK modulation output FSKOUT.                                                                                                                                                                                                                                                                                                                                                                            |

| 13 | PAGND  |                                       | Ground connection for the power amplifier (PA).<br>All the RF ground path of the power amplifier<br>should be concentrated to this pin.                                                                                                                                                                                                                                                                                        |

Infineon technologies

Funct\_Block.wmf

Wireless Components

Infineon

#### **Contents of this Chapter**

| 4.1 | Antenna              |

|-----|----------------------|

| 4.2 | Reference Oscillator |

| 4.3 | Frequency stability  |

| 4.4 | Modulation           |

| 4.5 | Lock time            |

| 4.6 | Clock output         |

#### 4.1 Antenna

The antenna used for the application board is a special loop configuration design. It utilizes an unusual capacitive loading at the end of the loop. Simulations and tests have proved this antenna to be more efficient and haveing a wider bandwidth than a conventional antenna grounded at its end. This effect is partly caused by radiation of additional electrical field components by the loop itself. The antenna in this case should not be considered as a mere magnetic loop but rather as a certain part of a dipole. Placing it apart from the electronic part on the board forms kind a of dipole antenna. The hot part of the loop - now primarily at its end - radiates certain electrical field components which add to the magnetic component.

The radiation resistance of a small loop of area A with a uniform current distribution can be calculated as

$$R_{\rm B} = 320 \ \pi^4 \ {\rm A}^2/\lambda^4$$

The inductance of a single turn loop having a circumference of U and a wire diameter of d is

$$L_{I} = 0.2 U (In U/d - 1.07)$$

The unloaded  $Q_U = X_L/R_R$  of such a loop is quite high in practice. The antenna configuration on the application board results in a typical *lossless*

$Q_U \approx 150 \ \Omega$  / 9.5 m $\Omega$  = 15400

at 434Mhz. Adding the losses of the loop will reduce this value to

It is at least by one order of magnitude higher then the Q of the components being used in the matching circuit. Therefore matching will be done to the losses of the components and not to  $R_R$  itself. The best matching circuit will then be the one presenting the designed load to the power amplifier while giving the highest current through  $L_L$ . The current through  $L_L$  is  $Q_L$  times the input current to the tank circuit. The loaded  $Q_L$  should be kept high in order to achieve a high antenna efficiency.  $Q_L$  should be kept down to a realistic value, however, to avoid tuning problems with a too narrow band resonance circuit.

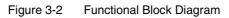

The power amplifier operates in a high efficient class C mode. This mode is characterized by a pulsed operation of the power amplifier transistor at a current flow angel of  $\Theta \le \pi$ . A frequency selective network at the amplifier output passes the fundamental frequency component of the pulse spectrum of the collector current to the load. The load and its resonance transformation to the collector of the power amplifier can be generalized by the equivalent circuit of Figure 4-1. The tank circuit L//C//R<sub>L</sub> in parallel to the output impedance of the transistor should be in resonance at the operating frequency of the transmitter.

Equivalent-power.wmf

Figure 4-1 Equivalent power amplifier tank circuit

The optimum load at the collector of the power amplifier for "critical" operation under idealized conditions at resonance is:

$$R_{LC} = V_S^2 / 2 P_o.$$

A typical value of  $R_{LC}$  for a RF output power of  $P_0$ = 5mW is:

$$R_{IC} = (2.7V)^2 / 10mW = 729\Omega.$$

"Critical" operation is characterized by the RF peak voltage swing at the collector of the PA transistor to just reach the supply voltage  $V_S$ . The high degree of efficiency under "critical" operating conditions can be explained by the low power losses at the transistor.

During the conducting phase of the transistor there will be present no or only a very small collector voltage. This way the power losses of the transistor, equal to  $i_C u_{CE}$ , will be minimized. This is particularly true for low current flow angels of  $\Theta << \pi$ .

In practice the RF-saturation voltage of the PA transistor and other parasitics will reduce the "critical"  $\rm R_{LC}.$

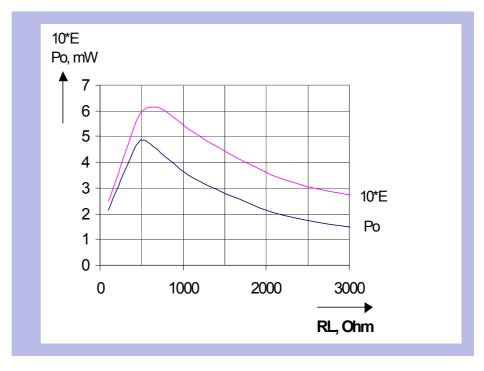

The output power P<sub>o</sub> will be reduced when operating in an "overcritical" mode at a  $R_L > R_{LC}$ . As shown in Figure 4-2, however, power efficiency E (and bandwidth) will increase by some degree when operating at higher  $R_L$ . The collector efficiency E is defined as

$$E = P_o / V_s * I_c$$

The diagram of Figure 4-2 has been derived from a test circuit having losses of 1.0dB within the matching network. Taking this into account, the corrected efficiency will be  $E_{max}=~0.76\cong76\%\,$  at its maximum.

The DC collector current Ic of the power amplifier and the RF output power  $P_o$  vary with the load resistor  $R_L$ . This is typical for overcritical operation of class C amplifiers.

Power\_output.wmf

Figure 4-2 Output power Po (mW) and collector efficiency E vs. load resistor R<sub>L</sub>.

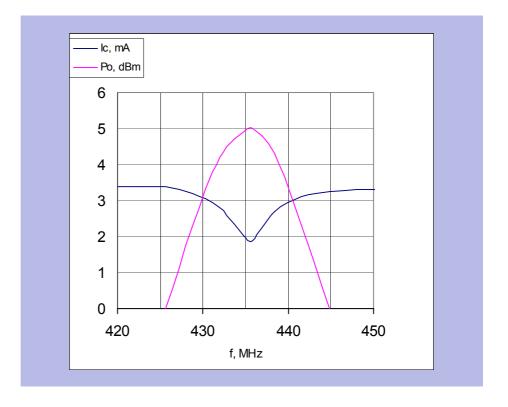

The collector current will show a characteristic dip at the resonance frequency for this type of "overcritical" operation. The depth of this dip will increase with higher values of  $\mathsf{R}_{\mathsf{L}}$ .

As Figure 4-3 shows, detuning beyond the bandwidth of the antenna circuit results in a significant increase in collector current of the power amplifier and in some loss of output power. This diagram shows the data for the circuit of the test board, Figure 5-1 at the frequency of 435.4 MHz. The effective load resistor of this circuit is  $R_L$ = 900 $\Omega$ .

This is two times the value of a "critical" class C operation, which has been found to be  $R_{LC} = 470 \Omega$  for the PA transistor of the TDA5100 at a supply voltage of  $V_S = 2.7V$ .

power\_vs\_frq.wmf

Figure 4-3 Power output and collector current vs. frequency

The loaded Q of the antenna on the evaluation PCB  $~(Q_L\approx 40$  at 434MHz and  $Q_L\approx 25$  at 869MHz) is quite high. A tuning-free realization requires a careful design of the components within the matching network.

The resonance frequency of the antenna circuit should be kept within its 3dB points at the operating frequency even under worst case conditions for the tolerance of the components involved. Placing the DC path for the collector voltage L1 at the end of the antenna in parallel to C3 allows some fine-tuning of the antenna by a matching L1//C3 combination.

Finding the worst case tolerances of the components will be demonstrated for an example at the more critical frequency of 434 MHz. A loaded  $Q_L = 40$  corresponds to a bandwidth of:

$B = 434MHz/Q_L = 10.8 MHz = \pm 5.4 MHz.$

The resonance frequency of a LC circuit follows a (LC)<sup>-1/2</sup> law. Thus:

$-\Delta f/f = \frac{1}{2} \quad \Delta C/C = \frac{1}{2} \quad \Delta L/L = \pm \frac{1}{2}Q_L.$

The tolerance requirements for L or C can be calculated as:

$\Delta C/C = \Delta L/L = \pm 1/Q_1 = \pm 2.5 \%.$

If the resonance frequency is determined equally by the C and L components, the tolerances under worst case conditions add up, resulting in a tolerance requirement for L and C of just  $\pm 1.25$  % each.

The above calculation of the tolerance requirements has been done for a LC parallel tank circuit. Therefore the result directly applies to C2 of the application board. The L component of the tank circuit in the application board is formed by the combination of C3 //L1 in series to the inductance of the antenna loop. Hence, the tolerance requirements for C3 will be less stringent. A good CAE tool can help to design the antenna circuit.

The final design of C2, C3 and L1 must be done on the PCB. This empirical design is the only way to cover all the effects which influence the antenna and the matching circuit. In a first step the components given for the evaluation board may be imparted. Tuning C3 will give the characteristic drop of the DC collector current of the PA transistor at the resonance point of the tank circuit. A deeper drop will be achieved for lower values of C2. A current drop by app. 20% seems to be a good compromise for output power, power efficiency and ease of tuning. As seen in Figure 4-2, a 20% drop in collector current will be achieved by a load resistor of  $R_L \approx 900\Omega$ . Next, the antenna matching network requires adjusting the C3//L1 combination. A tuning free realization of the tank circuit requires a very precise loading at the end of the antenna loop. In general this can not be realized by applying just one capacitor with a standard value. Either two capacitors or a capacitor in parallel to an inductor have to be used to tune the antenna resonance precisely to the operating frequency of the transmitter. The inductance L1 should compensate a small part of the capacity C3 only. This avoids additional losses within the matching network due to the quite low Q of the inductors being used.

Suppression of the radiation of spurious harmonics may require some additional filtering within the antenna matching circuit.

The effective radiated power of the application transmitter board has been measured to be -9dBm ERP at a 434MHz frequency and -4dBm ERP at 869MHz.

| Table 4-1                 |                   |                   |                                                     |  |

|---------------------------|-------------------|-------------------|-----------------------------------------------------|--|

| Frequency                 | ERP at<br>434 MHz | ERP at<br>869 MHz | regulations,<br>limit<br>ETS 300 220<br>434/869 MHz |  |

| Carrier f <sub>C</sub>    | - 9 dBm           | -4 dBm            | +10 dBm                                             |  |

| f <sub>C</sub> + 13.5 MHz | -75 dBm           | -51dBm            | -36 dBm                                             |  |

| f <sub>C</sub> – 13.5 MHz | -73 dBm           | -59 dBm           | -36/-54 dBm                                         |  |

| f <sub>C</sub> ± 847 kHz  | -62 dBm           | - 67 dBm          | -36 dBm                                             |  |

| 2 <sup>nd</sup> harmonic  | -51dBm            | -56 dBm           | -36/-30 dBm                                         |  |

| 3 <sup>rd</sup> harmonic  | -42 dBm           | -72 dBm           | -30 dBm                                             |  |

The total radiated spectrum measured can be summarized as:

Utilizing higher efficiency antennas may bring up the radiated power to a level of 0 dBm ERP in both frequency bands. A very effective yet quite small antenna may be an inductively loaded stub. Its application is limited to non-handheld systems however. Absorption by a hand in close proximity will reduce its effectiveness by much more than can be observed with a magnetic antenna.

Care must be taken with all high efficiency antennas however to keep spurious radiation down below the limit level to achieve compliance with ETS 300 220. The most critical frequency under this aspect is the  $f_C - f_{ref}$  component. When operated at 869MHz, it may fall into the frequency band of  $\leq$  862MHz. According to ETS 300 220, spurious emissions shall not exceed a value of -54dBm below the frequency of 862MHz.

#### 4.2 Reference Oscillator

The transmitting frequency and its stability are determined by the reference crystal and its associated oscillator circuit.

The oscillator is of the negative impedance converter type: a resistor and a capacitor are "sign-inverted" to give a negative resistor in series with an inductor at the oscillator port cosc pin10.

The reference oscillator either operates at 6.78MHz or at 13.56MHz. The reference frequency will be given by

| f <sub>ref</sub>       | CSEL input   |

|------------------------|--------------|

| f <sub>VCO</sub> / 64  | High or open |

| f <sub>VCO</sub> / 128 | Low          |

The transmitting frequency  $f_C$  is identical to the frequency  $f_{VCO}$  of the internal VCO for operation at 869MHz. For operation at 434MHz the frequency  $f_{VCO}$  will be divided by two, resulting in the transmitter output frequency.

The S-parameters of the oscillator circuit presented in Table 4-2 have been taken at pin10 of the TDA 5100 on the evaluation board under load conditions when oscillation just starts up. The characteristic impedance of the given S-parameters is  $Z_0 = 1k\Omega$ . The inductance of the equivalent input impedance varies to quite some extends with the load conditions of the oscillator however. At the operating frequency of 13.57 MHz the inductance changes from 13.94 µH under max. load conditions to 10.2 µH for a high-Q, lossless loading.

| Table 4-2 S-Parameters of the Reference Oscillator |                     |                    |                 |                |

|----------------------------------------------------|---------------------|--------------------|-----------------|----------------|

| f (MHz)                                            | S11 (Z <sub>0</sub> | <sub>D</sub> =1kΩ) | Equivalent Impe | dance Elements |

| 2.0                                                | 8.64                | 38.8°              | 13.85 μH        | -1184 Ω        |

| 4.0                                                | 5.33                | 55.4°              | 14.95 μH        | -1173 Ω        |

| 6.0                                                | 3.69                | 66.1°              | 15.37 μH        | -1084 Ω        |

| 6.78                                               | 3.30                | 67.0°              | 15.31 μH        | -1062 Ω        |

| 8.0                                                | 2.79                | 69.6°              | 15.20 μH        | -991 Ω         |

| 10.0                                               | 2.17                | 72.3°              | 14.97 μH        | -845 Ω         |

| 12.0                                               | 1.75                | 73.3°              | 14.50 μH        | -680 Ω         |

| 13.57                                              | 1.52                | 73.6°              | 13.94 μH        | -537 Ω         |

| 14.0                                               | 1.46                | 73.8°              | 13.77 μH        | -494 Ω         |

| 16.0                                               | 1.23                | 74.6°              | 12.66 μH        | -280 Ω         |

| 18.0                                               | 1.05                | 72.4°              | 12.06 μH        | -69 Ω          |

| 20.0                                               | 0.88                | 19.6°              | 11.30 μH        | +199 Ω         |

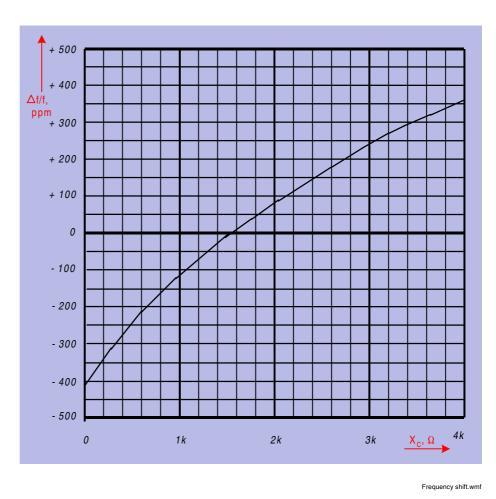

Figure 4-4 Frequency shift of the oscillator as a function of the impedance X<sub>C</sub> of the pulling Capacitor C6 on the application board

The frequency of the reference crystal oscillator is being pulled by the capacitor C6. Figure 4-4 shows the pulling effect by C6 for a frequency of 13.56MHz. C6 has been grounded at one side for this test. The diagram shows the frequency pulling effect as a function of the impedance  $X_C$  of the pulling capacitor. The values given have been taken on the evaluation board for a crystal having typical dynamic parameters.

They include the effect of the spurious capacity of the crystal to ground of 2.2pF. The reference frequency in the diagram (at 0 ppm) is specified as the resonance frequency of the crystal for the specified load capacitance of  $C_L = 20$ pF. As can be seen, the pulling range is quite large. This is typical for an oscillator circuit representing an inductive component to the crystal. The further the frequency is pulled down however, the more the frequency stability will degrade. As a design rule, the frequency should not be pulled down too far.

This keeps the frequency tolerance and the temperature drift, caused by the characteristics of the internal inductive component of the TDA5100 (not including the crystal itself), low.

The total capacitive load to the oscillator port should be kept below 10pF. Otherwise spurious oscillation may arise at the resonance frequency of this capacitance with the internal inductive component of the TDA5100.

The design of the oscillator circuit can be implemented on the basis of the above information. As a practical design rule Figure 4-4 can be used to find the values of C6 and C7 and the ordering specification of the crystal.

For ASK operation of the transmitter, C7 will be replaced by a short. C6 can be grounded then, and pin11 can be left open. As a first design step, C6 can be calculated from Table 4-2. The effective load-impedance represented to the crystal is given by adding the impedances of C6 and the internal inductance of the oscillator circuit as given in Table 4-2. C6 has to be chosen to sum up with the internal inductance to the designed load capacitance of the crystal. To compensate for the parasitics, a fine tuning of C6 has to be done for the final layout on the PCB.

| Design Example:    |                                                                                                            |

|--------------------|------------------------------------------------------------------------------------------------------------|

| Transmit frequency | 868.40 MHz                                                                                                 |

| Modulation         | ASK                                                                                                        |

| Crystal            | $f_c = f_{tx} / 64 = 13.56875 \text{ MHz},$<br>load capacitance $C_L = 20 \text{ pF},$<br>fundamental mode |

According to Table 4-2, the inductance of the oscillator circuit under max. load conditions is  $L_{XO} = 13.94 \ \mu H \cong + j1188 \ \Omega$ . Loaded with a high-Q-crystal, the inductance will rather be 10.5  $\mu H \cong + j895\Omega$ . The designed load capacitance of the crystal is  $C_L = 20pF \cong -j586\Omega$ . So, the effective capacitance to be placed in series with the crystal will be given by:

The stray capacitance of the crystal to ground is 2.2 pF in total. Adding half of it at each port of the crystal to the oscillator circuit will give a final value of C6 of

$$C6 = 6.5 \, \text{pF}$$

A more accurate design of C6 can be done on produced basis of Figure 4-4. This function has been taken for different values of C6 from the evaluation board. It therefor includes all the parasitics to be effective on the board.

According to Figure 4-4, C6 has to be

$X_{C6} = -j1440 \Omega$ C6 = 8.15 pF

to get the oscillator to the designed resonance frequency of the crystal.

As can be seen from Figure 4-4, the slope of the graph at the resonance point is +180 ppm/k $\Omega$ . Thus, a variation of the capacitance by  $\pm 0.1$ pF  $\cong \pm j20 \Omega$  results in a frequency offset error of  $\pm 3.6$  ppm  $\cong \pm 3.1$  kHz at a frequency of 869MHz.

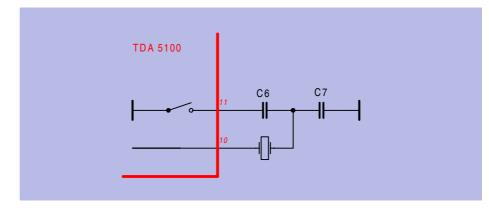

FSK modulation is achieved by frequency modulation of the reference oscillator. The switch at FSKOUT, pin11 is operated by the modulating signal, being DC coupled. During the closed state the frequency-determining capacitor is C6. During the open state a capacitor C7 is added in series with C6, increasing the frequency by an amount equal two times the frequency shift. The On/Off state of the switch at pin11 has the characteristic impedance of:

$\begin{array}{rcl} Z_{on}: & 120 \ \Omega \ // \ 6 p F & (for \ 6.8 MHz) \\ & 120 \ \Omega \ // \ 3.5 p F & (for \ 13.57 MHz) \\ Z_{off}: & 12 k \Omega \ // \ 2.5 p F \end{array}$

A logic high at the FSK input FSKDTA pin7 results in an open switch and hence in a frequency being determined by C6 in series with C7. A logic low closes the switch and reduces the frequency to a value given by C6. As a first design step, the values for C6 and C7 giving the desired center frequency and frequency deviation can be taken from Figure 4-4.

The value of C6 can be found at a frequency higher than the center frequency by the designed frequency deviation. The value of C7 to be put in series with C6 will be found at the frequency point lower than the center frequency by the designed frequency deviation. In order to compensate for the parasitics of the PCB, a fine tuning of C6 and C7 has to be done for the final layout on the board.

| Design Example:    |                                                                                                                                                                                                       |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit frequency | 868.40 MHz                                                                                                                                                                                            |

| Modulation         | FSK, frequency deviation ± 20kHz                                                                                                                                                                      |

| Crystal            | $\label{eq:fc} \begin{array}{l} f_c = f_{tx}  / 64 \ = 13.56875 \ \text{MHz}, \\ \text{load capacitance } C_L = 20 \text{pF} \ \cong \text{-j586} \ \Omega, \\ & \text{fundamental mode} \end{array}$ |

The lower frequency state is determined by C6. This frequency should be lower than the center frequency by the designed frequency deviation of -20 kHz/868.4 MHz = -23 ppm. As can be seen from Figure 4-4, the capacitor C6 will be

$X_{C6} = -j1.44 \text{ k}\Omega + j1 \text{k}\Omega * 23 \text{ppm}/180 \text{ppm} = -j1.32 \text{ k}\Omega$ C6 = 8.88 pF.

At the high frequency state the shift by +46ppm related to the lower frequency state will be given by adding a capacitor of

$X_{C7}$ = -j1 k $\Omega$  \* 46ppm/180ppm = -j255  $\Omega$ C7 = 46 pF

in series with C6. Subtracting the capacitance of the open switch at pin 10 yields

$$C7 = 46 \text{ pF} - 2.5 \text{ pF} = 43.5 \text{ pF}$$

Both the design examples for ASK and for FSK modulation have been done for a crystal being specified for a load capacitance of  $C_L=20$  pF. This specification is well suited for a reliable design of the reference oscillator. The range of  $C_L$  is limited by the practicability of the capacitors C6 and C7 and the susceptability of the oscillator to induced noise for too low values. The resultant values for C6 and C7 can be obtained with low tolerances. The capacitor C6 determines the center frequency of the transmitter. It can be specified for a tolerance of  $\pm 0.1$  pF. It has been shown that this will result in a frequency error of  $\pm 3.1$  kHz at a frequency within the 869MHz band.

All the above calculations have been done for the more economical crystals in the 13.57 MHz frequency range. The design rules can be applied to crystals at 6.8 MHz as well.

As a general and more practical design rule for C6 and C7, the following procedure may apply:

- Choose a crystal for the designed frequency with a nominal load capacitance of CL=10pF to CL=20pF.

- Determine the value of C6 on the board for a documented crystal to get the designed carrier frequency for a transmitter being ASK-modulated.

- For a transmitter being FSK-modulated, C6 has to be chosen to get a frequency lower than the carrier frequency by the designed frequency deviation. The FSK switch (pin11) has to be kept closed during this process. While the FSK switch is open, C7 will be added to give a frequency just higher than the designed carrier frequency by the FSK frequency deviation.

- If the capacitance of C6 and C7 can not be realized by standard values, adding two capacitors in series or in parallel will give a combination which allows a tuning-free design.

- This procedures applies for crystals at 6.8 MHz and 13.7 MHz.

Inverted\_fsk.wmf

According to Figure 4-5, the phase of modulation can be inverted by switching a capacitor C6 in parallel with C7 and not in series. This design is recommended for systems operating at a large FSK frequency deviation. The oscillator is more equally stable then for both the frequency states. The phase of the baseband signal in the receiver has to be adapted to the transmitted signal.

#### 4.3 Frequency stability

The frequency stability of the transmitter is affected by a number of factors:

- Tuning tolerance of the crystal

- Temperature stability of the crystal

- Aging of the crystal

- Tuning tolerance of the oscillator circuit

- Tuning stability of the oscillator circuit

- Detuning of the oscillator due to nearby obstacles

- Detuning of the oscillator due to RF feedback

- Operating voltage

- Temperature stability of the oscillator circuit

In the following table an assessment of the worst case overall frequency spread to be expected in case of operation at 868MHz with a 13.56875MHz Tokyo Denpa reference crystal as denoted in the Bill of Materials in Table 4-3 is shown. The calculation is taking into account the tolerance of the crystal and of the components in the oscillator circuit which are determining the tuning tolerance and temperature stability of the circuit. Note that the result is a sum of the squares of the indivual terms.

A spreadsheet<sup>1</sup> may be obtained from Infineon which can be used to predict the total frequency error under worst-case conditions by simply entering the crystal specification.

| Table 4-3 Assessment of the Worst Case Frequency Error of the Crystal     Oscillator |                                                                                                                           |         |  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------|--|

| Tolerance of the crystal                                                             | ······································                                                                                    |         |  |

|                                                                                      | temperature stability ±20ppm                                                                                              | ± 20ppm |  |

| Tolerance of the circuit                                                             | tolerance of the series load capacitor $C_V$ $\pm 2\%$                                                                    | ±8ppm   |  |

|                                                                                      | tolerance of the oscillator circuit (3 $\sigma$ spread of internal component values assumed), calculated with spreadsheet | ±48ppm  |  |

|                                                                                      | Total frequency spread under worst-case conditions                                                                        | ± 63ppm |  |

1.available for download on the Infineon RKE Webpage www.infineon.com/rke, also included on evalkit CD-ROM

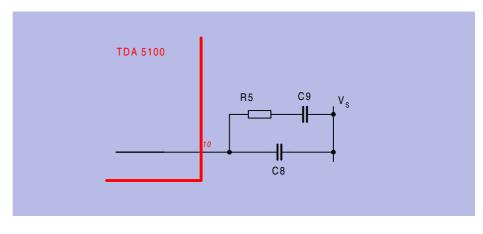

#### 4.4 Modulation

A stand alone encoder device has been imparted to the transmitter board. The encoder chip HCS 360 (Microchip) is used as a signal source to modulate the transmitter either in ASK or in FSK mode. The code-hopping data sequence of the HCS 360 is band-limited by an RC low pass filter (4.7 k $\Omega$  with 4.7 nF) at a cutoff frequency of 7.2 kHz before it is applied to the modulation input of the TDA 5100.

The logic of the power-up function at the modulation inputs of the TDA 5100 allows some different modes of interfacing to the encoder and the actuator key. Power-down mode at a very low standby current will be held if both the ASK and the FSK modulation inputs (pin6 and pin7) and the PDWN input, pin 1 are at a low state. A high state at the PDWN input will power up the internal device. A logic high or an open at one of the modulation inputs will internally supply a pullup current to the PDWN input. This will power up the device under an open condition at the PDWN input. A low at the PDWN input, pin 1 will force the device to the off state. The supply current will be  $40\mu$ A then if one of the modulation input is at a logic high state.

| Mode of     | PDWN Input | Modulation Input |            |  |  |

|-------------|------------|------------------|------------|--|--|

| Operation   |            | ASKDTA           | FSKDTA     |  |  |

| Power down  | L, open    | L                | L          |  |  |

| Off State   | L          | Н                | Н          |  |  |

| CW, carrier | H, open    | Н                | H, L, open |  |  |

| ASK         | H, open    | Data             | Н          |  |  |

| FSK         | H, open    | н                | Data       |  |  |

The low voltage detect output will be pulled down if the supply voltage falls below the trigger level of 2.15 V. The output configuration is a open collector common emitter stage. It can be used as a warning input signal to the controller or to shut down the transmitter if a critical low voltage situation is reached. In both modes of modulation the shut-off function can be easily realized by pulling down the ASK modulation input by the low voltage detect signal. A series resistor will decouple the output to the encoder.

The interface circuit on the evaluation board had to be adapted to the specific encoder being used. Pin6 of the encoder chip has to be kept at a low state during the power-up sequence. This avoids blocking of the encoder due to a false signal at its I/O pin6 during power-up.

Load pulling of the VCO frequency by the PA will result in quite some residual FSK modulation when the PA is ASK modulated. The frequency deviation will be as much as 3MHz peak. The duration of this frequency step is limited by the reaction time of the PLL to app. 10 $\mu$ s. The output spectrum of the transmitter will show some spurious content within a band of  $\pm$ 3MHz to the carrier frequency. The spectral density will increase with higher ASK data rates.

In order to comply with the regulations for spurious emition, the data rate as to be kept below 10KB/s in practice.

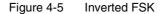

The noise spectrum of the transmitter at a carrier frequency at 869MHz is shown in Figure 4-6.

It is measured with a resolution bandwidth of 10 kHz. It shows the typical noise suppression within the loop bandwidth of 150 kHz. Sideband noise of the VCO outside the loop bandwidth at  $\pm$  200 kHz can be specified at -91dBc/Hz.

Noise 869.wmf

Figure 4-6 Noise spectrum at 869MHz

#### 4.5 Lock time

The lock-up time of the transmitter includes both the start-up time of the crystal oscillator and the PLL lock time. The circuit has been designed to minimize both times.

The time constant of the start-up process of the reference oscillator is given by

$$\tau = 2Q / \Delta v \omega$$

As can be seen, the start-up time  $t_S\approx 20~^{\star}\tau$  is inversely proportional to the bandwidth of the crystal. A 13.5 MHz oscillator therefore will start twice as fast as a 6.7 MHz oscillator assuming a constant crystal Q. By using a 13.5 MHz crystal and the 64 prescaler, the start-up time of the crystal oscillator can be cut in half over that achieved by the 6.7MHz crystal oscillator circuit. As can be seen from Table 2-1, the excessive gain  $\Delta v$  of the oscillator has been designed for a very high value within the TDA 5100. Experimentally, a power-up start-up time for the oscillator of  $T_S$ = 600  $\mu s$  has been recorded using 13.5 MHz crystals.

The PLL lock time  $~t_L~$  is related to the PLL natural frequency  $\omega_n~~$  by  $~t_L\approx 10$  /  $\omega_n~$

The internal loop filter to the TDA 5100 has been designed for a natural frequency of

$\omega_n = 2\pi \ 150 \text{ kHz}.$

The resultant lock time will be  $t_L \approx 10 \ \mu s$ .

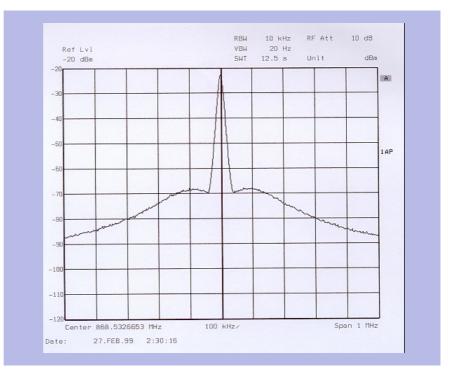

To obtain maximum flexibility in the system design the characteristics of the loop can be modified externally by adding a second-order RC loop filter. As can be seen from Figure 4-7 it consists of two capacitors and a resistor in a shunt configuration at pin4. It will reduce the natural loop frequency to a design value.

The characteristic parameters of the PLL are:

| VCO tuning sensitivity | K <sub>VCC</sub> | <sub>D</sub> = 55 MHz / V |

|------------------------|------------------|---------------------------|

| Phase detector gain    | $K_\Phi$         | = 30 µA / rad             |

| Division ratio         | Ν                | = 64 (13.5MHz)            |

|                        | Ν                | = 128 (6,8 MHz)           |

External\_loop.wmf

Figure 4-7 Optional external loop filter for reduced loop bandwidth

FSK modulation is imparted directly to the reference oscillator. The VCO has to be fast enough to follow the frequency variations within the loop. As the primary consideration, the modulation rate needs to be much lower than the PLL bandwidth to enable the PLL to track the modulation. In practice, the PLL bandwidth should be at least five to ten times higher than the maximum data rate input to the modulator.

#### 4.6 Clock output

The clock output CLKOUT, pin 8 can be configured to supply a clock signal to a microcontroller. The frequency of the clock signal is fixed to the values:

| Table 4-4       |                |

|-----------------|----------------|

| Clock frequency | CLKDIV input   |

| 3.39 MHz        | Low            |

| 847.5 kHz       | High (or open) |

The clock output is a open collector configuration. This will reduce DC power consumption to zero if it is not used. A external pull up resistor  $R_{CL}$  has to be applied to drive the clock input of the microcontroller. It has to be designed to drive the effective load capacitance  $C_{CL}$  (microcontroller input and wiring capacitance) at a low to high signal transition:

$$R_{CL} \leq 1 / 8*C_{CL}*f_{CL}$$

$\ensuremath{\mathsf{R}_{\text{CL}}}$  should be designed as high as possible in order to reduce overall DC power consumption.

#### **Contents of this Chapter**

| 5.1 | Application Circuit                    | . 5-2 |

|-----|----------------------------------------|-------|

| 5.2 | Test Board Layouts.                    | . 5-3 |

| 5.3 | Bill of material (Application Circuit) | . 5-4 |

| 5.4 | Application Board                      | . 5-5 |

## 5.1 Application Circuit

Application\_circuit.wmf

## 5.2 Test Board Layouts

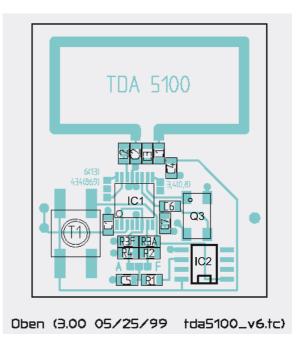

Figure 5-2 Top Side of TDA 5100

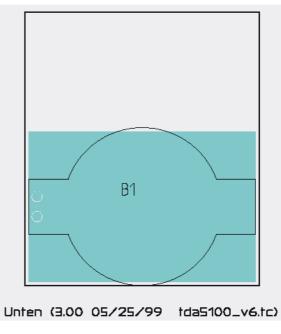

Figure 5-3 Bottom Side of TDA 5100

| 5.3 | Bill of material (Application Circuit) |  |

|-----|----------------------------------------|--|

|-----|----------------------------------------|--|

| Table 5-1 Bill of material |                         |         |         |       |       |                                                        |

|----------------------------|-------------------------|---------|---------|-------|-------|--------------------------------------------------------|

| Part                       | Value                   | 434 MHz | 869 MHz | ASK   | FSK   | Specification                                          |

|                            |                         |         |         |       |       |                                                        |

| R1                         | 4.7 kΩ                  |         |         |       |       | 0805, ± 5%                                             |

| R2                         |                         |         |         |       | 12 kΩ | 0805, ± 5%                                             |

| R3A                        |                         |         |         | 15 kΩ |       | 0805, ± 5%                                             |

| R3F                        |                         |         |         |       | 15 kΩ | 0805, ± 5%                                             |

| R4                         | 15 kΩ                   |         |         |       |       | 0805, ± 5%                                             |

| C1                         | 47 nF                   |         |         |       |       | 0805,X7R, ±10%                                         |

| C2                         |                         | 8.2 pF  | 1.5 pF  |       |       | 0805, COG, ± 5%                                        |

| C3                         |                         | 4.7 pF  | 1.0 pF  |       |       | 0805, COG, ± 0.1 pF                                    |

| C4                         | 100 pF                  |         |         |       |       | 0805, COG, ± 5%                                        |

| C5                         | 4.7 nF                  |         |         |       |       | 0805,X7R, ±10%                                         |

| C6                         | 8.2 pF                  |         |         |       |       | 0805, COG, ± 0.1 pF                                    |

| C7                         |                         | 22 pF   | 47 pF   | 0Ω    |       | 0805, COG, ± 5%<br>0805 0Ω Jumper                      |

| L1                         |                         | 100 nH  | 27 nH   |       |       | TOKO LL2012-J                                          |

| L2                         |                         | 0Ω      | 22 nH   |       |       | 0Ω resistor bridge<br>22nH: TOKO LL1608-J              |

| Q3                         | 13.56875 MHz<br>CL=20pF |         |         |       |       | Tokyo Denpa TSS-3B<br>13568.75kHz<br>Spec.No. 20-18906 |

| IC1                        | TDA5100                 |         |         |       |       |                                                        |

| IC2                        | HCS360                  |         |         |       |       | Microchip                                              |

| B1                         | Batteriehalter          |         |         |       |       | HU2031-1, RENATA                                       |

| T1                         | Taster                  |         |         |       |       | STTSKHMPW, ALPS                                        |

Reference

## 5.4 Application Board

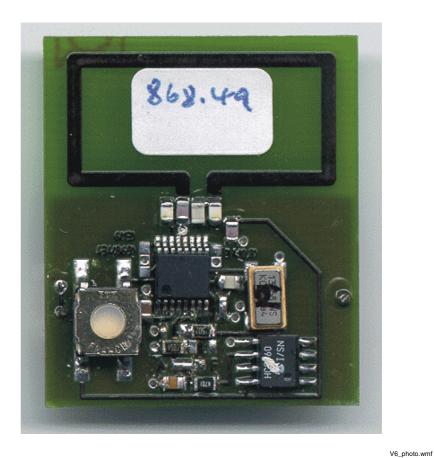

Figure 5-4 Photo of Application Board TDA5100

Reference