# In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) Guide

All rights reserved. Copyright © 2000, Microchip Technology Incorporated, USA. Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights." The Microchip name and logo, PIC, PICmicro, PRO MATE, PICSTART, MPLAB, and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Inc. in the U.S.A. and other countries.

In-Circuit Serial Programming and ICSP are trademarks and SQTP is a service mark of Microchip Technology Inc.

All other trademarks mentioned herein are property of their respective companies.

### **Table of Contents**

#### PAGE

| SECTION 1 | INTRODUCTION                                                 |      |

|-----------|--------------------------------------------------------------|------|

| In-Circ   | uit Serial Programming™ (ICSP™) Guide                        |      |

| SECTION 2 | TECHNICAL BRIEFS                                             |      |

| How to    | Implement ICSP™ Using PIC12C5XX OTP MCUs                     | 2-1  |

| How to    | Implement ICSP™ Using PIC16CXXX OTP MCUs                     |      |

| How to    | Implement ICSP™ Using PIC17CXXX OTP MCUs                     |      |

| How to    | Implement ICSP™ Using PIC16F8X FLASH MCUs                    | 2-21 |

| SECTION 3 | PROGRAMMING SPECIFICATIONS                                   |      |

| In-Circ   | uit Serial Programming for PIC12C5XX OTP MCUs                |      |

| In-Circ   | uit Serial Programming for PIC12C67X and PIC12CE67X OTP MCUs |      |

| In-Circ   | uit Serial Programming for PIC14000 OTP MCUs                 |      |

| In-Circ   | uit Serial Programming for PIC16C55X OTP MCUs                |      |

| In-Circ   | uit Serial Programming for PIC16C6XX/7XX/9XX OTP MCUs        |      |

| In-Circ   | uit Serial Programming for PIC17C7XX OTP MCUs                |      |

|           | uit Serial Programming for PIC18CXXX OTP MCUs                |      |

| In-Circ   | uit Serial Programming for PIC16F62X FLASH MCUs              |      |

|           | uit Serial Programming for PIC16F8X FLASH MCUs               |      |

|           | uit Serial Programming for PIC16F8XX FLASH MCUs              |      |

#### SECTION 4 APPLICATION NOTES

In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) of Calibration Parameters Using a PICmicro<sup>®</sup> Microcontroller ......4-1

# SECTION 1 INTRODUCTION

# INTRODUCTION

### In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) Guide

# WHAT IS IN-CIRCUIT SERIAL PROGRAMMING (ICSP)?

In-System Programming (ISP) is a technique where a programmable device is programmed after the device is placed in a circuit board.

In-Circuit Serial Programming (ICSP) is an enhanced ISP technique implemented in Microchip's PICmicro<sup>®</sup> One-Time-Programmable (OTP) and FLASH RISC microcontrollers (MCU). Use of only two I/O pins to serially input and output data makes ICSP easy to use and less intrusive on the normal operation of the MCU.

Because they can accommodate rapid code changes in a manufacturing line, PICmicro OTP and FLASH MCUs offer tremendous flexibility, reduce development time and manufacturing cycles, and improve time to market.

### In-Circuit Serial Programming enhances the flexibility of the PICmicro even further.

This *In-Circuit Serial Programming Guide* is designed to show you how you can use ICSP to get an edge over your competition. Microchip has helped its customers implement ICSP using PICmicro MCUs since 1992. Contact your local Microchip sales representative today for more information on implementing ICSP in your product.

#### PICmicro MCUs MAKE IN-CIRCUIT SERIAL PROGRAMMING A CINCH

Unlike many other MCUs, most PICmicro MCUs offer a simple serial programming interface using only two I/O pins (plus power, ground and  $V_{PP}$ ). Following very simple guidelines, these pins can be fully utilized as I/O pins during normal operation and programming pins during ICSP.

ICSP can be activated through a simple 5-pin connector and a standard PICmicro programmer supporting serial programming mode such as Microchip's PRO MATE<sup>®</sup> II.

No other MCU has a simpler and less intrusive Serial Programming Mode to facilitate your ICSP needs.

# WHAT CAN I DO WITH IN-CIRCUIT SERIAL PROGRAMMING?

ICSP is truly an enabling technology that can be used in a variety of ways including:

#### Reduce Cost of Field Upgrades

The cost of upgrading a system's code can be dramatically reduced using ICSP. With very little effort and planning, a PICmicro OTP- or FLASH-based system can be designed to have code updates in the field.

For PICmicro FLASH devices, the entire code memory can be rewritten with new code. In PICmicro OTP devices, new code segments and parameter tables can be easily added in program memory areas left blank for update purpose. Often, only a portion of the code (such as a key algorithm) requires update.

#### Reduce Time to Market

In instances where one product is programmed with different customer codes, generic systems can be built and inventoried ahead of time. Based on actual mix of customer orders, the PICmicro MCU can be programmed using ICSP, then tested and shipped. The lead-time reduction and simplification of finished goods inventory are key benefits.

#### Calibrate Your System During Manufacturing

Many systems require calibration in the final stages of manufacturing and testing. Typically, calibration parameters are stored in Serial EEPROM devices. Using PICmicro MCUs, it is possible to save the additional system cost by programming the calibration parameters directly into the program memory.

#### Add Unique ID Code to Your System During Manufacturing

Many products require a unique ID number or a serial number. An example application would be a remote keyless entry device. Each transmitter has a unique "binary key" that makes it very easy to program in the access code at the very end of the manufacturing process and prior to final test.

Serial number, revision code, date code, manufacturer ID and a variety of other useful information can also be added to any product for traceability. Using ICSP, you can eliminate the need for DIP switches or jumpers.

In-Circuit Serial Programming and ICSP are trademarks of Microchip Technology Inc. SQTP is a service mark of Microchip Technology Inc.

In fact, this capability is so important to many of our customers that Microchip offers a factory programming service called Serialized Quick Turn Programming (SQTP<sup>SM</sup>), where each PICmicro MCU device is coded with up to 16 bytes of unique code.

#### Calibrate Your System in the Field

Calibration need not be done only in the factory. During installation of a system, ICSP can be used to further calibrate the system to actual operating environment.

In fact, recalibration can be easily done during periodic servicing and maintenance. In OTP parts, newer calibration data can be written to blank memory locations reserved for such use.

#### Customize and Configure Your System in the Field

Like calibration, customization need not done in the factory only. In many situations, customizing a product at installation time is very useful. A good example is home or car security systems where ID code, access code and other such information can be burned in after the actual configuration is determined. Additionally, you can save the cost of DIP switches and jumpers, which are traditionally used.

### • Program Dice When Using Chip-On-Board (COB)

If you are using COB, Microchip offers a comprehensive die program. You can get dice that are preprogrammed, or you may want to program the die once the circuit board is assembled. Programming and testing in one single step in the manufacturing process is simpler and more cost effective.

#### PROGRAMMING TIME CONSIDERATIONS

Programming time can be significantly different between OTP and FLASH MCUs. OTP (EPROM) bytes typically program with pulses in the order of several hundred microseconds. FLASH, on the other hand, require several milliseconds or more per byte (or word) to program.

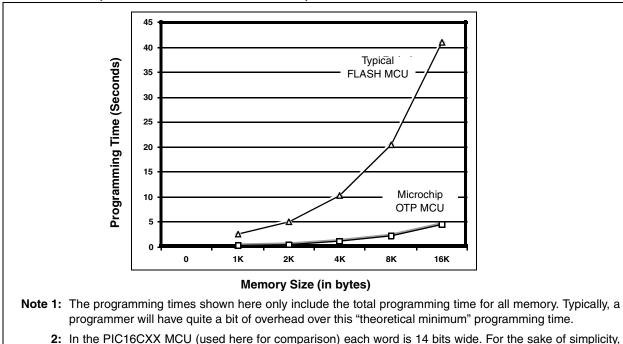

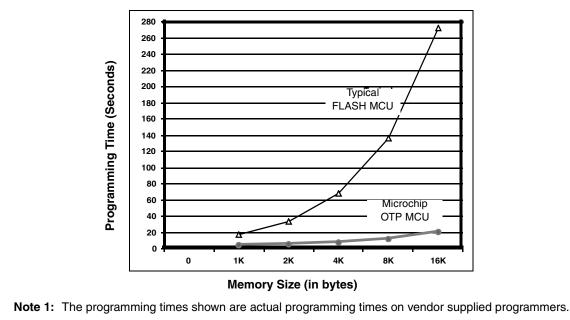

Figure 1 and Figure 2 below illustrate the programming time differences between OTP and FLASH MCUs. Figure 1 shows programming time in an ideal programmer or tester, where the only time spent is actually programming the device. This is only important to illustrate the minimum time required to program such devices, where the programmer or the tester is fully optimized.

Figure 2 is a more realistic programming time comparison, where the "overhead" time for programmer or a tester is built in. The programmer often requires 3 to 5 times the "theoretically" minimum programming time.

FIGURE 1: PROGRAMMING TIME FOR FLASH AND OTP MCUS (THEORETICAL MINIMUM TIMES)

FIGURE 2: PROGRAMMING TIME FOR FLASH AND OTP MCUS (TYPICAL PROGRAMMING TIMES ON A PROGRAMMER)

2: Microchip OTP programming times are based on PRO MATE II programmer.

#### Ramifications

The programming time differences between FLASH and OTP MCUs are not particular material for prototyping quantities. However, its impact can be significant in large volume production.

# MICROCHIP PROVIDES A COMPLETE SOLUTION FOR ICSP

#### Products

Microchip offers the broadest line of ICSP-capable MCUs:

- PIC12C5XX OTP, 8-pin Family

- PIC12C67X OTP, 8-pin Family

- PIC12CE67X OTP, 8-pin Family

- PIC16C6XX OTP, Mid-Range Family

- PIC17C7XX OTP High-End Family

- PIC18CXXX OTP, High-End Family

- PIC16F62X FLASH, Mid-Range Family

- PIC16F8X FLASH, Mid-Range Family

- PIC6F8XX FLASH, Mid-Range Family

All together, Microchip currently offers over 40 MCUs capable of ICSP.

#### **Development Tools**

Microchip offers a comprehensive set of development tools for ICSP that allow system engineers to quickly prototype, make code changes and get designs out the door faster than ever before.

PRO MATE II Production Programmer – a production quality programmer designed to support the Serial Programming Mode in MCUs up to midvolume production. PRO MATE II runs under DOS in a Command Line Mode, Microsoft<sup>®</sup> Windows<sup>®</sup> 3.1, Windows<sup>®</sup> 95/98, and Windows NT<sup>®</sup>. PRO MATE II is also capable of Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>), where each device can be programmed with up to 16 bytes of unique code.

Microchip offers an ICSP kit that can be used with the Universal Microchip Device Programmer, PRO MATE II. Together these two tools allow you to implement ICSP with minimal effort and use the ICSP capability of Microchip's PICmicro MCUs.

#### **Technical support**

Microchip has been delivering ICSP capable MCUs since 1992. Many of our customers are using ICSP capability in full production. Our field and factory application engineers can help you implement ICSP in your product.

# Introduction

NOTES:

# SECTION 2 TECHNICAL BRIEFS

| HOW TO IMPLEMENT ICSP™ USING PIC12C5XX OTP MCUS  | 2-1  |

|--------------------------------------------------|------|

| HOW TO IMPLEMENT ICSP™ USING PIC16CXXX OTP MCUS  | 2-9  |

| HOW TO IMPLEMENT ICSP™ USING PIC17CXXX OTP MCUS  | 2-15 |

| HOW TO IMPLEMENT ICSP™ USING PIC16F8X FLASH MCUS | 2-21 |

### How to Implement ICSP<sup>TM</sup> Using PIC12C5XX OTP MCUs

Author: Thomas Schmidt Microchip Technology Inc.

#### INTRODUCTION

The technical brief describes how to implement in-circuit serial programming<sup>™</sup> (ICSP) using the PIC12C5XX OTP PICmicro<sup>®</sup> MCU.

ICSP is a simple way to manufacture your board with an unprogrammed PICmicro MCU and program the device just before shipping the product. Programming the PIC12C5XX MCU in-circuit has many advantages for developing and manufacturing your product.

- Reduces inventory of products with old firmware. With ICSP, the user can manufacture product without programming the PICmicro MCU. The PICmicro MCU will be programmed just before the product is shipped.

- ICSP in production. New software revisions or additional software modules can be programmed during production into the PIC12C5XX MCU.

- **ICSP in the field.** Even after your product has been sold, a service man can update your program with new program modules.

- One hardware with different software. ICSP allows the user to have one hardware, whereas the PIC12C5XX MCU can be programmed with different types of software.

- Last minute programming. Last minute programming can also facilitate quick turnarounds on custom orders for your products.

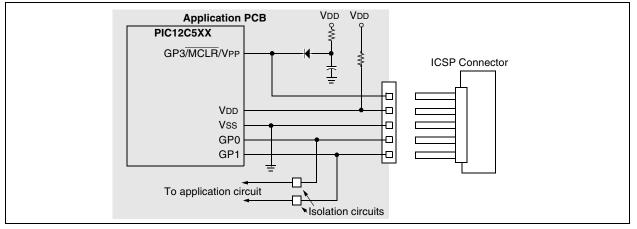

#### FIGURE 1: TYPICAL APPLICATION CIRCUIT

#### IN-CIRCUIT SERIAL PROGRAMMING

To implement ICSP into an application, the user needs to consider three main components of an ICSP system: Application Circuit, Programmer and Programming Environment.

#### **Application Circuit**

During the initial design phase of the application circuit, certain considerations have to be taken into account. Figure 1 shows and typical circuit that addresses the details to be considered during design. In order to implement ICSP on your application board you have to put the following issues into consideration:

- 1. Isolation of the GP3/MCLR/VPP pin from the rest of the circuit.

- 2. Isolation of pins GP1 and GP0 from the rest of the circuit.

- 3. Capacitance on each of the VDD, GP3/MCLR/ VPP, GP1, and GP0 pins.

- 4. Interface to the programmer.

- 5. Minimum and maximum operating voltage for VDD.

PICmicro, PRO MATE and PICSTART are registered trademarks of Microchip Technology Inc. In-Circuit Serial Programming and ICSP are trademarks of Microchip Technology Inc.

#### Isolation of the GP3/MCLR/VPP Pin from the Rest of the Circuit

PIC12C5XX devices have two ways of configuring the MCLR pin:

- MCLR can be connected either to an external RC circuit or

- MCLR is tied internally to VDD

When GP3/MCLR/VPP pin is connected to an external RC circuit, the pull-up resistor is tied to VDD, and a capacitor is tied to ground. This circuit can affect the operation of ICSP depending on the size of the capacitor.

Another point of consideration with the GP3/MCLR/VPP pin, is that when the PICmicro MCU is programmed, this pin is driven up to 13V and also to ground. Therefore, the application circuit must be isolated from the voltage coming from the programmer.

When MCLR is tied internally to VDD, the user has only to consider that up to 13V are present during programming of the GP3/MCLR/VPP pin. This might affect other components connected to that pin.

For more information about configuring the GP3/ MCLR/VPP internally to VDD, please refer to the PIC12C5XX data sheet (DS40139).

#### Isolation of Pins GP1 and GP0 from the Rest of the Circuit

Pins GP1 and GP0 are used by the PICmicro MCU for serial programming. GP1 is the clock line and GP0 is the data line.

GP1 is driven by the programmer. GP0 is a bidirectional pin that is driven by the programmer when programming and driven by the PICmicro MCU when verifying. These pins must be isolated from the rest of the application circuit so as not to affect the signals during programming. You must take into consideration the output impedance of the programmer when isolating GP1 and GP0 from the rest of the circuit. This isolation circuit must account for GP1 being an input on the PICmicro MCU and for GP0 being bidirectional pin.

For example, PRO MATE<sup>®</sup> II has an output impedance of 1 k $\Omega$ . If the design permits, these pins should not be used by the application. This is not the case with most designs. As a designer, you must consider what type of circuitry is connected to GP1 and GP0 and then make a decision on how to isolate these pins.

#### Total Capacitance on VDD, GP3/MCLR/VPP, GP1, and GP0

The total capacitance on the programming pins affects the rise rates of these signals as they are driven out of the programmer. Typical circuits use several hundred microfarads of capacitance on VDD, which helps to dampen noise and improve electromagnetic interference. However, this capacitance requires a fairly strong driver in the programmer to meet the rise rate timings for VDD.

#### Interface to the Programmer

Most programmers are designed to simply program the PICmicro MCU itself and don't have strong enough drivers to power the application circuit.

One solution is to use a driver board between the programmer and the application circuit. The driver board needs a separate power supply that is capable of driving the VPP, VDD, GP1, and GP0 pins with the correct ramp rates and also should provide enough current to power-up the application circuit.

The cable length between the programmer and the circuit is also an important factor for ICSP. If the cable between the programmer and the circuit is too long, signal reflections may occur. These reflections can momentarily cause up to twice the voltage at the end of the cable, that was sent from the programmer. This voltage can cause a latch-up. In this case, a termination resistor has to be used at the end of the signal line.

## Minimum and Maximum Operating Voltage for VDD

The PIC12C5XX programming specification states that the device should be programmed at 5V. Special considerations must be made if your application circuit operates at 3V only. These considerations may include totally isolating the PICmicro MCU during programming. The other point of consideration is that the device must be verified at minimum and maximum operation voltage of the circuit in order to ensure proper programming margin.

For example, a battery driven system may operate from three 1.5V cells giving an operating voltage range of 2.7V to 4.5V. The programmer must program the device at 5V and must verify the program memory contents at both 2.7V and 4.5V to ensure that proper programming margins have been achieved.

#### THE PROGRAMMER

PIC12C5XX MCUs only use serial programming and, therefore, all programmers supporting these devices will support the ICSP. One issue with the programmer is the drive capability. As discussed before, it must be able to provide the specified rise rates on the ICSP signals and also provide enough current to power the application circuit. It is recommended that you buffer the programming signals.

Another point of consideration for the programmer is what VDD levels are used to verify the memory contents of the PICmicro MCU. For instance, the PRO MATE II verifies program memory at the minimum and maximum VDD levels for the specified device and is therefore considered a production quality programmer. On the other hand, the PICSTART<sup>®</sup> Plus only verifies at 5V and is for prototyping use only. The PIC12C5XX programming specifications state that the program memory contents should be verified at both the minimum and maximum VDD levels that the application circuit will be operating. This implies that the application circuit must be able to handle the varying VDD voltages.

There are also several third-party programmers that are available. You should select a programmer based on the features it has and how it fits into your programming environment. The *Microchip Development Systems Ordering Guide* (DS30177) provides detailed information on all our development tools. The *Microchip Third Party Guide* (DS00104) provides information on all of our third party development tool developers. Please consult these two references when selecting a programmer. Many options exist including serial or parallel PC host connection, stand-alone operation, and single or gang programmers.

#### **PROGRAMMING ENVIRONMENT**

The programming environment will affect the type of programmer used, the programmer cable length, and the application circuit interface. Some programmers are well suited for a manual assembly line while others are desirable for an automated assembly line. A gang programmer should be chosen for programming multiple MCUs at one time. The physical distance between the programmer and the application circuit affects the load capacitance on each of the programming signals. This will directly affect the drive strength needed to provide the correct signal rise rates and current. Finally, the application circuit interface to the programmer depends on the size constraints of the application circuit itself and the assembly line. A simple header can be used to interface the application circuit to the programmer. This might be more desirable for a manual assembly line where a technician plugs the programmer cable into the board.

A different method is the uses spring loaded test pins (often referred as pogo-pins). The application circuit has pads on the board for each of the programming signals. Then there is a movable fixture that has pogo pins in the same configuration as the pads on the board. The application circuit is moved into position and the fixture is moved such that the spring loaded test pins come into contact with the board. This method might be more suitable for an automated assembly line.

After taking into consideration the issues with the application circuit, the programmer, and the programming environment, anyone can build a high quality, reliable manufacturing line based on ICSP.

#### **OTHER BENEFITS**

ICSP provides several other benefits such as calibration and serialization. If program memory permits, it would be cheaper and more reliable to store calibration constants in program memory instead of using an external serial EEPROM.

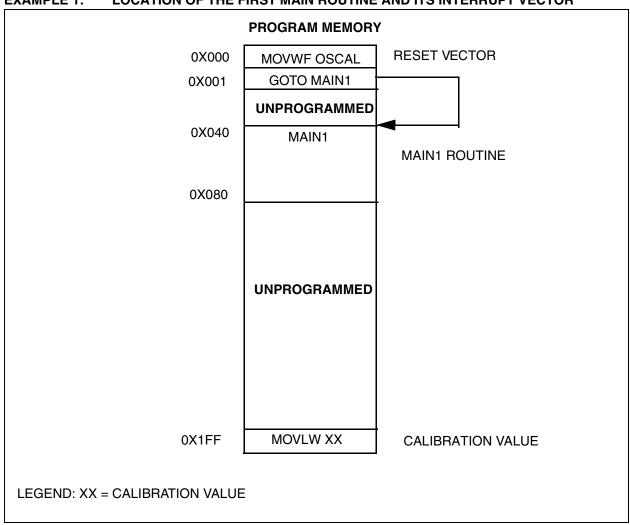

#### Field Programming of PICmicro OTP MCUs

An OTP device is not normally capable of being reprogrammed, but the PICmicro MCU architecture gives you this flexibility provided the size of your firmware is less than half that of the desired device.

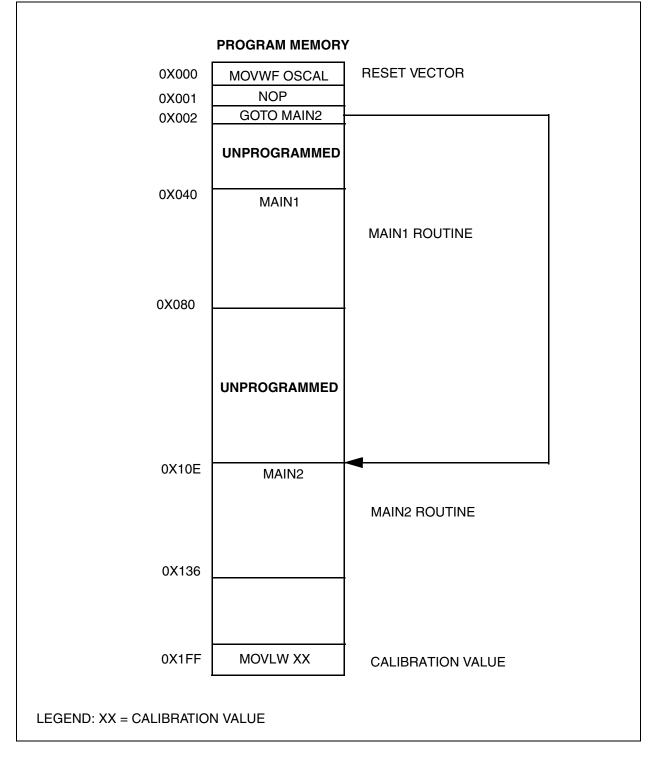

This method involves using jump tables for the reset and interrupt vectors. Example 1 shows the location of a main routine and the reset vector for the first time a device with 0.5K-words of program memory is programmed. Example 2 shows the location of a second main routine and its reset vector for the second time the same device is programmed. You will notice that the GOTO Main that was previously at location 0x0002 is replaced with an NOP. An NOP is a program memory location with all the bits programmed as 0s. When the reset vector is executed, it will execute an NOP and then a GOTO Main1 instruction to the new code.

#### EXAMPLE 2: LOCATION OF THE SECOND MAIN ROUTINE AND IT INTERRUPT VECTOR (AFTER SECOND PROGRAMMING)

Since the program memory of the PIC12C5XX devices is organized in 256 x 12 word pages, placement of such information as look-up tables and CALL instructions must be taken into account. For further information, please refer to application note *AN581*, *Implementing Long Calls* and application note *AN556*, *Implementing a Table Read*.

#### CONCLUSION

Microchip Technology Inc. is committed to supporting your ICSP needs by providing you with our many years of experience and expertise in developing in-circuit system programming solutions. Anyone can create a reliable in-circuit system programming station by coupling our background with some forethought to the circuit design and programmer selection issues previously mentioned. Your local Microchip representative is available to answer any questions you have about the requirements for ICSP.

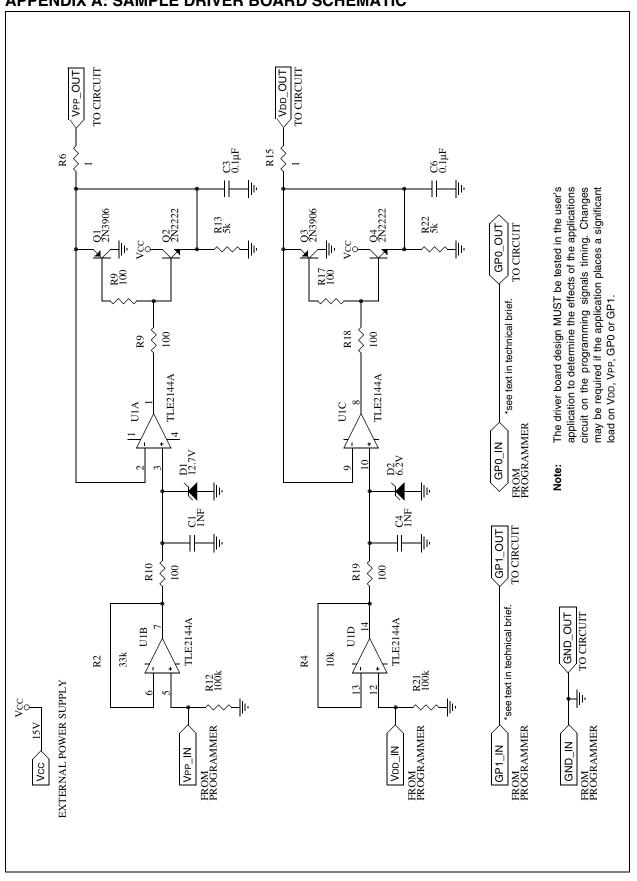

#### **APPENDIX A: SAMPLE DRIVER BOARD SCHEMATIC**

NOTES:

### How to Implement ICSP<sup>TM</sup> Using PIC16CXXX OTP MCUs

Author: Rodger Richey Microchip Technology Inc.

#### INTRODUCTION

In-Circuit Serial Programming<sup>™</sup> (ICSP) is a great way to reduce your inventory overhead and time-to-market for your product. By assembling your product with a blank Microchip microcontroller (MCU), you can stock one design. When an order has been placed, these units can be programmed with the latest revision of firmware, tested, and shipped in a very short time. This method also reduces scrapped inventory due to old firmware revisions. This type of manufacturing system can also facilitate quick turnarounds on custom orders for your product.

Most people would think to use ICSP with PICmicro<sup>®</sup> OTP MCUs only on an assembly line where the device is programmed once. However, there is a method by which an OTP device can be programmed several times depending on the size of the firmware. This method, explained later, provides a way to field upgrade your firmware in a way similar to EEPROM- or Flash-based devices.

#### HOW DOES ICSP WORK?

Now that ICSP appeals to you, what steps do you take to implement it in your application? There are three main components of an ICSP system: Application Circuit, Programmer and Programming Environment.

#### **Application Circuit**

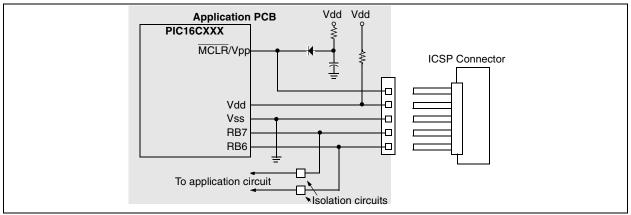

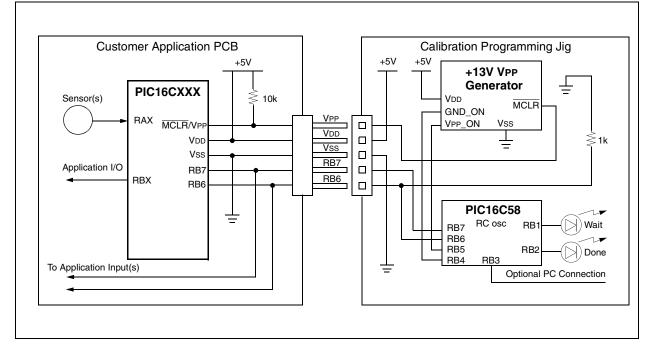

The application circuit must be designed to allow all the programming signals to be directly connected to the PICmicro MCU. Figure 1 shows a typical circuit that is a starting point for when designing with ICSP. The application must compensate for the following issues:

- Isolation of the MCLR/V<sub>PP</sub> pin from the rest of the circuit.

- Isolation of pins RB6 and RB7 from the rest of the circuit.

- Capacitance on each of the VDD, MCLR/V<sub>PP</sub>, RB6, and RB7 pins.

- 4. Minimum and maximum operating voltage for VDD.

- 5. PICmicro Oscillator.

- 6. Interface to the programmer.

The  $\overline{\text{MCLR}/V_{\text{PP}}}$  pin is normally connected to an RC circuit. The pull-up resistor is tied to VDD and a capacitor is tied to ground. This circuit can affect the operation of ICSP depending on the size of the capacitor. It is, therefore, recommended that the circuit in Figure 1 be used when an RC is connected to  $\overline{\text{MCLR}/V_{\text{PP}}}$ . The diode should be a Schottky-type device. Another issue with  $\overline{\text{MCLR}/V_{\text{PP}}}$  is that when the PICmicro MCU device is programmed, this pin is driven to approximately 13V and also to ground. Therefore, the application circuit must be isolated from this voltage provided by the programmer.

#### FIGURE 1: TYPICAL APPLICATION CIRCUIT

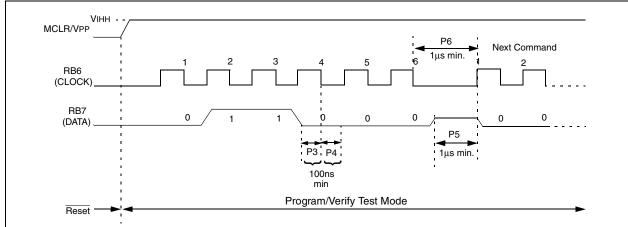

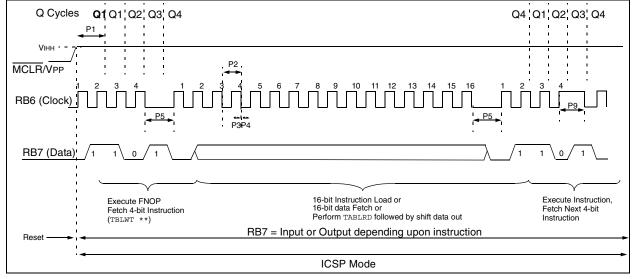

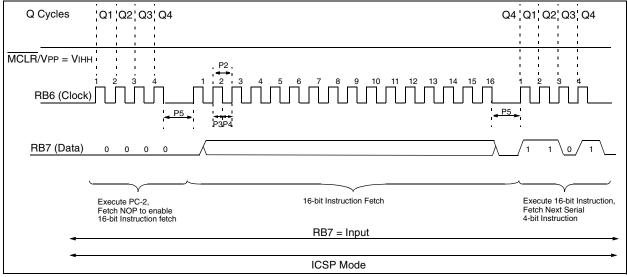

Pins RB6 and RB7 are used by the PICmicro MCU for serial programming. RB6 is the clock line and RB7 is the data line. RB6 is driven by the programmer. RB7 is a bidirectional pin that is driven by the programmer when programming, and driven by the PICmicro MCU when verifying. These pins must be isolated from the rest of the application circuit so as not to affect the signals during programming. You must take into consideration the output impedance of the programmer when isolating RB6 and RB7 from the rest of the circuit. This isolation circuit must account for RB6 being an input on the PICmicro MCU, and for RB7 being bidirectional (can be driven by both the PICmicro MCU and the programmer). For instance, PRO MATE® II has an output impedance of 1k34. If the design permits, these pins should not be used by the application. This is not the case with most applications so it is recommended that the designer evaluate whether these signals need to be buffered. As a designer, you must consider what type of circuitry is connected to RB6 and RB7 and then make a decision on how to isolate these pins. Figure 1 does not show any circuitry to isolate RB6 and RB7 on the application circuit because this is very application dependent.

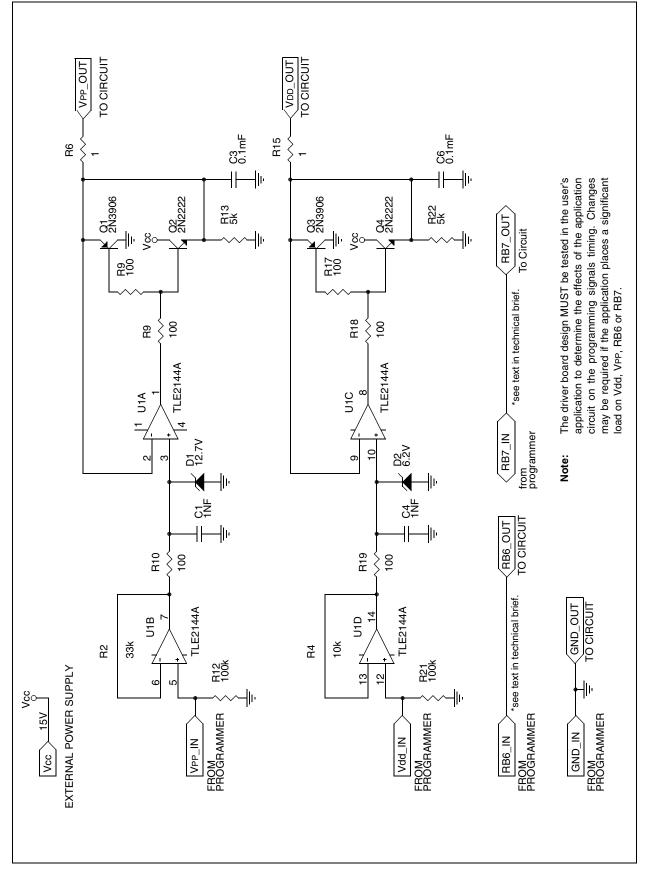

The total capacitance on the programming pins affects the rise rates of these signals as they are driven out of the programmer. Typical circuits use several hundred microfarads of capacitance on VDD which helps to dampen noise and ripple. However, this capacitance requires a fairly strong driver in the programmer to meet the rise rate timings for VDD. Most programmers are designed to simply program the PICmicro MCU itself and don't have strong enough drivers to power the application circuit. One solution is to use a driver board between the programmer and the application circuit. The driver board requires a separate power supply that is capable of driving the VPP and VDD pins with the correct rise rates and should also provide enough current to power the application circuit. RB6 and RB7 are not buffered on this schematic but may require buffering depending upon the application. A sample driver board schematic is shown in Appendix A.

**Note:** The driver board design MUST be tested in the user's application to determine the effects of the application circuit on the programming signals timing. Changes may be required if the application places a significant load on VDD, VPP, RB6 OR RB7.

The Microchip programming specification states that the device should be programmed at 5V. Special considerations must be made if your application circuit operates at 3V only. These considerations may include totally isolating the PICmicro MCU during programming. The other issue is that the device must be verified at the minimum and maximum voltages at which the application circuit will be operating. For instance, a battery operated system may operate from three 1.5V cells giving an operating voltage range of 2.7V to 4.5V. The programmer must program the device at 5V and must verify the program memory contents at both 2.7V and 4.5V to ensure that proper programming margins have been achieved. This ensures the PICmicro MCU option over the voltage range of the system.

This final issue deals with the oscillator circuit on the application board. The voltage on MCLR/VPP must rise to the specified program mode entry voltage before the device executes any code. The crystal modes available on the PICmicro MCU are not affected by this issue because the Oscillator Start-up Timer waits for 1024 oscillations before any code is executed. However, RC oscillators do not require any startup time and, therefore, the Oscillator Startup Timer is not used. The programmer must drive MCLR/VPP to the program mode entry voltage before the RC oscillator toggles four times. If the RC oscillator toggles four or more times, the program counter will be incremented to some value X. Now when the device enters programming mode, the program counter will not be zero and the programmer will start programming your code at an offset of X. There are several alternatives that can compensate for a slow rise rate on MCLR/VPP. The first method would be to not populate the R, program the device, and then insert the R. The other method would be to have the programming interface drive the OSC1 pin of the PICmicro MCU to ground while programming. This will prevent any oscillations from occurring during programming.

Now all that is left is how to connect the application circuit to the programmer. This depends a lot on the programming environment and will be discussed in that section.

#### Programmer

The second consideration is the programmer. PIC16CXXX MCUs only use serial programming and therefore all programmers supporting these devices will support ICSP. One issue with the programmer is the drive capability. As discussed before, it must be able to provide the specified rise rates on the ICSP signals and also provide enough current to power the application circuit. Appendix A shows an example driver board. This driver schematic does not show any buffer circuitry for RB6 and RB7. It is recommended that an evaluation be performed to determine if buffering is required. Another issue with the programmer is what VDD levels are used to verify the memory contents of the PICmicro MCU. For instance, the PRO MATE II verifies program memory at the minimum and maximum VDD levels for the specified device and is therefore considered a production quality programmer. On the other hand, the PICSTART<sup>®</sup> Plus only verifies at 5V and is for prototyping use only. The Microchip programming specifications state that the program memory contents should be verified at both the minimum and maximum VDD levels that the application circuit will be operating. This implies that the application circuit must be able to handle the varying VDD voltages.

There are also several third party programmers that are available. You should select a programmer based on the features it has and how it fits into your programming environment. The *Microchip Development Systems Ordering Guide* (DS30177) provides detailed information on all our development tools. The *Microchip Third Party Guide* (DS00104) provides information on all of our third party tool developers. Please consult these two references when selecting a programmer. Many options exist including serial or parallel PC host connection, stand-alone operation, and single or gang programmers. Some of the third party developers include Advanced Transdata Corporation, BP Microsystems, Data I/O, Emulation Technology and Logical Devices.

#### **Programming Environment**

The programming environment will affect the type of programmer used, the programmer cable length, and the application circuit interface. Some programmers are well suited for a manual assembly line while others are desirable for an automated assembly line. You may want to choose a gang programmer to program multiple systems at a time.

The physical distance between the programmer and the application circuit affects the load capacitance on each of the programming signals. This will directly affect the drive strength needed to provide the correct signal rise rates and current. This programming cable must also be as short as possible and properly terminated and shielded, or the programming signals may be corrupted by ringing or noise.

Finally, the application circuit interface to the programmer depends on the size constraints of the application circuit itself and the assembly line. A simple header can be used to interface the application circuit to the programmer. This might be more desirable for a manual assembly line where a technician plugs the programmer cable into the board. A different method is the use of spring loaded test pins (commonly referred to as pogo pins). The application circuit has pads on the board for each of the programming signals. Then there is a fixture that has pogo pins in the same configuration as the pads on the board. The application circuit or fixture is moved into position such that the pogo pins come into contact with the board. This method might be more suitable for an automated assembly line.

After taking into consideration the issues with the application circuit, the programmer, and the programming environment, anyone can build a high quality, reliable manufacturing line based on ICSP.

#### **Other Benefits**

ICSP provides other benefits, such as calibration and serialization. If program memory permits, it would be cheaper and more reliable to store calibration constants in program memory instead of using an external serial EEPROM. For example, your system has a thermistor which can vary from one system to another. Storing some calibration information in a table format allows the microcontroller to compensate in software for external component tolerances. System cost can be reduced without affecting the required performance of the system by using software calibration techniques. But how does this relate to ICSP? The PICmicro MCU has already been programmed with firmware that performs a calibration cycle. The calibration data is transferred to a calibration fixture. When all calibration data has been transferred, the fixture places the PICmicro MCU in programming mode and programs the PICmicro MCU with the calibration data. Application note AN656, In-Circuit Serial Programming of Calibration Parameters Using a PICmicro Microcontroller, shows exactly how to implement this type of calibration data programming.

The other benefit of ICSP is serialization. Each individual system can be programmed with a unique or random serial number. One such application of a unique serial number would be for security systems. A typical system might use DIP switches to set the serial number. Instead, this number can be burned into program memory, thus reducing the overall system cost and lowering the risk of tampering.

#### Field Programming of PICmicro OTP MCUs

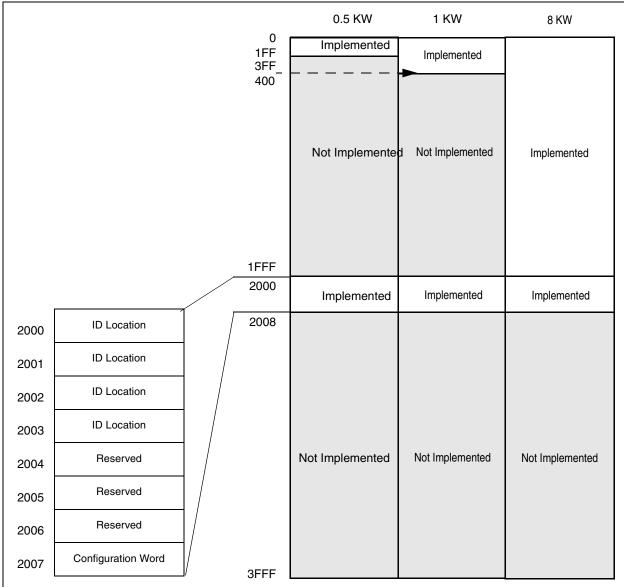

An OTP device is not normally capable of being reprogrammed, but the PICmicro MCU architecture gives you this flexibility provided the size of your firmware is at least half that of the desired device and the device is not code protected. If your target device does not have enough program memory, Microchip provides a wide spectrum of devices from 0.5K to 8K program memory with the same set of peripheral features that will help meet the criteria.

The PIC16CXXX microcontrollers have two vectors, reset and interrupt, at locations 0x0000 and 0x0004. When the PICmicro MCU encounters a reset or interrupt condition, the code located at one of these two locations in program memory is executed. The first listing of Example 1 shows the code that is first programmed into the PICmicro MCU. The second listing of Example 1 shows the code that is programmed into the PICmicro MCU.

#### EXAMPLE 1: PROGRAMMING CYCLE LISTING FILES

First Program Cycle

Second Program Cycle

| Proq | Opcode | Assembly                   | Prog | Opcode | Assembly                   |

|------|--------|----------------------------|------|--------|----------------------------|

| Mem  | -      | Instruction                |      |        | -                          |

|      |        |                            |      |        |                            |

| 0000 | 2808   | goto Main ;Main loop       |      |        |                            |

| 0001 | 3FFF   | <blank> ;at 0x0008</blank> | 0001 | 2860   | goto Main ;Main now        |

| 0002 | 3FFF   | <blank></blank>            | 0002 | 3FFF   | <blank> ;at 0x0060</blank> |

| 0003 | 3FFF   | <blank></blank>            | 0003 | 3FFF   | <blank></blank>            |

| 0004 | 2848   | goto ISR ;ISR at           | 0004 | 0000   | nop                        |

| 0005 | 3FFF   | <blank> ;0x0048</blank>    |      | 28A8   | goto ISR ;ISR now at       |

| 0006 | 3FFF   | <blank></blank>            | 0006 | 3FFF   | <blank> ;0x00A8</blank>    |

| 0007 | 3FFF   | <blank></blank>            | 0007 | 3FFF   | <blank></blank>            |

| 0008 | 1683   | bsf STATUS, RP0            |      | 0008   | 1683 bsf STATUS, RP0       |

| 0009 | 3007   | movlw 0x07                 | 0009 | 3007   | movlw 0x07                 |

| A000 | 009F   | movwf ADCON1               | A000 | 009F   | movwf ADCON1               |

|      |        |                            |      |        |                            |

|      |        |                            |      |        |                            |

|      |        |                            |      |        |                            |

| 0048 | 1C0C   | btfss PIR1,RBIF            | T.   |        | 1COC btfss PIR1,RBIF       |

| 0049 | 284E   | goto EndISR                | 0049 | 284E   | goto EndISR                |

| 004A | 1806   | btfsc PORTB,0              | 004A | 1806   | btfsc PORTB,0              |

|      |        |                            | j .  |        |                            |

|      |        |                            | j .  |        |                            |

|      |        |                            |      |        |                            |

| 0060 | 3FFF   | <blank></blank>            | 0060 | 1683   | bsf STATUS, RP0            |

| 0061 | 3FFF   | <blank></blank>            | 0061 | 3005   | movlw 0x05                 |

| 0062 | 3FFF   | <blank></blank>            | 0062 | 009F   | movwf ADCON1               |

|      |        |                            | j .  |        |                            |

|      |        |                            | ί.   |        |                            |

|      |        |                            | j.   |        |                            |

| 00A8 | 3FFF   | <blank></blank>            | 00A8 | 1C0C   | btfss PIR1,RBIF            |

| 00A9 | 3FFF   | <blank></blank>            | 00A9 | 28AE   | goto EndISR                |

| 00AA | 3FFF   | <blank></blank>            |      |        | btfsc PORTB,0              |

|      |        |                            |      |        |                            |

|      |        |                            | ί.   |        |                            |

|      |        |                            | j .  |        |                            |

|      |        |                            |      |        |                            |

|      |        |                            |      |        |                            |

The example shows that to program the PICmicro MCU a second time the memory location 0x0000, originally goto Main (0x2808), is reprogrammed to all 0's which happens to be a nop instruction. This location cannot be reprogrammed to the new opcode (0x2860) because the bits that are 0's cannot be reprogrammed to 1's, only bits that are 1's can be reprogrammed to 0's. The next memory location 0x0001 was originally blank (all 1's) and now becomes a goto Main (0x2860). When a reset condition occurs, the PICmicro MCU executes the instruction at location 0x0000 which is the nop, a completely benign instruction, and then executes the goto Main to start the execution of code. The example also shows that all program memory locations after 0x005A are blank in the original program so that the second time the PICmicro MCU is programmed, the revised code can be programmed at these locations. The same descriptions can be given for the interrupt vector at location 0x0004.

This method changes slightly for PICmicro MCUs with >2K words of program memory. Each of the goto Main and goto ISR instructions are replaced by the following code segments due to paging on devices with >2K words of program memory.

| movlw | <page></page> | movlw | <page></page> |

|-------|---------------|-------|---------------|

| movwf | PCLATH        | movwf | PCLATH        |

| goto  | Main          | goto  | ISR           |

Now your one time programmable PICmicro MCU is exhibiting more EEPROM- or Flash-like qualities.

#### CONCLUSION

Microchip Technology Inc. is committed to supporting your ICSP needs by providing you with our many years of experience and expertise in developing ICSP solutions. Anyone can create a reliable ICSP programming station by coupling our background with some forethought to the circuit design and programmer selection issues previously mentioned. Your local Microchip representative is available to answer any questions you have about the requirements for ICSP.

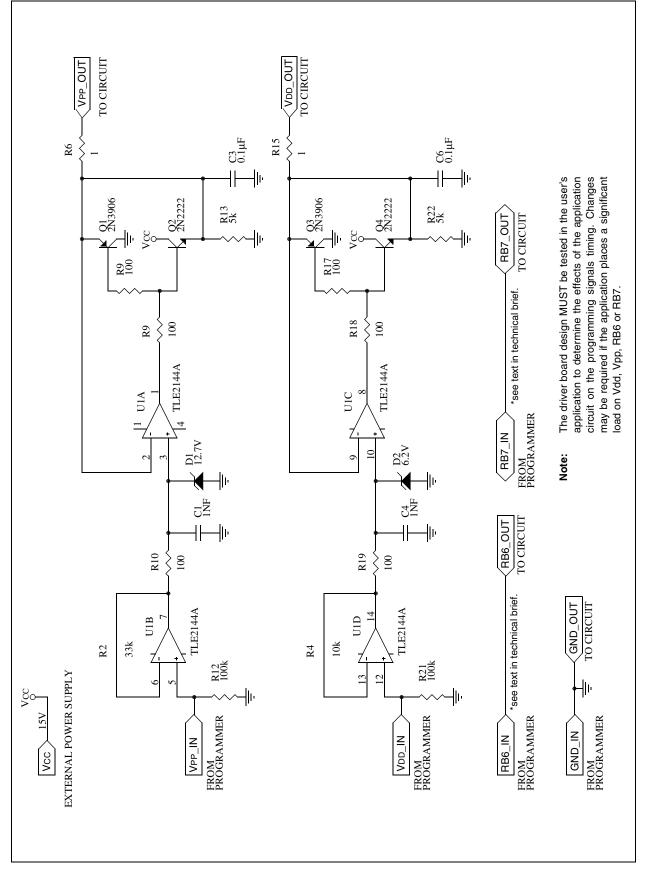

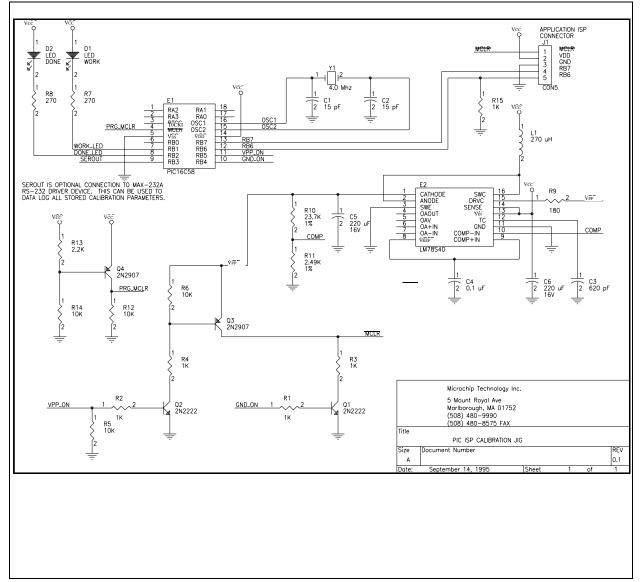

#### APPENDIX A: SAMPLE DRIVER BOARD SCHEMATIC

### How to Implement ICSP<sup>TM</sup> Using PIC17CXXX OTP MCUs

Author: Stan D'Souza Microchip Technology Inc.

#### INTRODUCTION

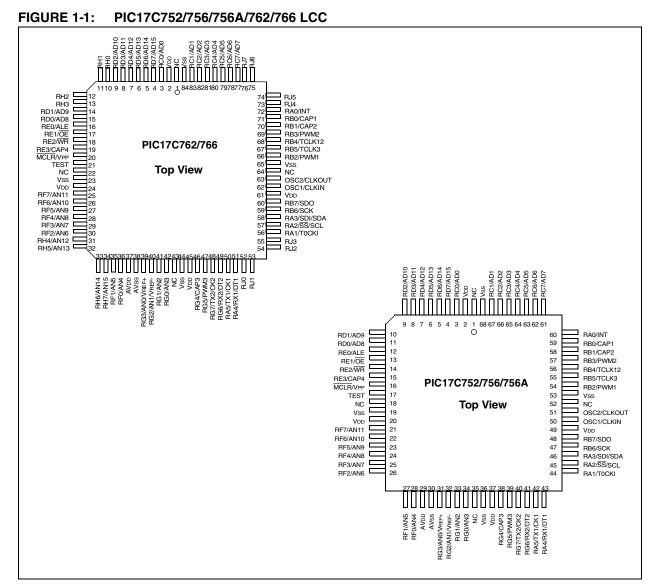

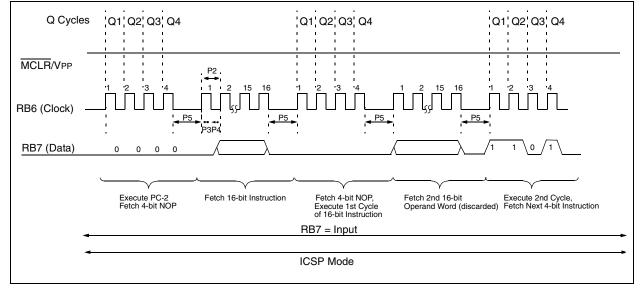

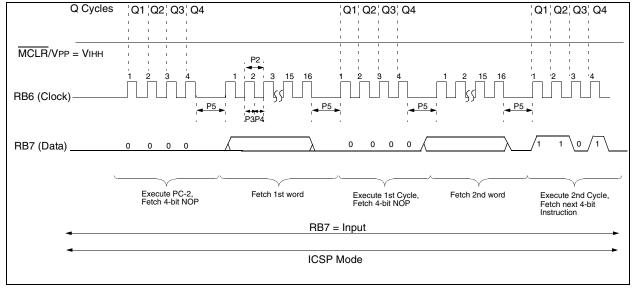

PIC17CXXX microcontroller (MCU) devices can be serially programmed using an RS-232 or equivalent serial interface. As shown in Figure 2, using just three pins, the PIC17CXXX can be connected to an external interface and programmed. In-Circuit Serial Programming (ICSP<sup>™</sup>) allows for a greater flexibility in an application as well as a faster time to market for the user's product.

This technical brief will demonstrate the practical aspects associated with ICSP using the PIC17CXXX. It will also demonstrate some key capabilities of OTP devices when used in conjunction with ICSP.

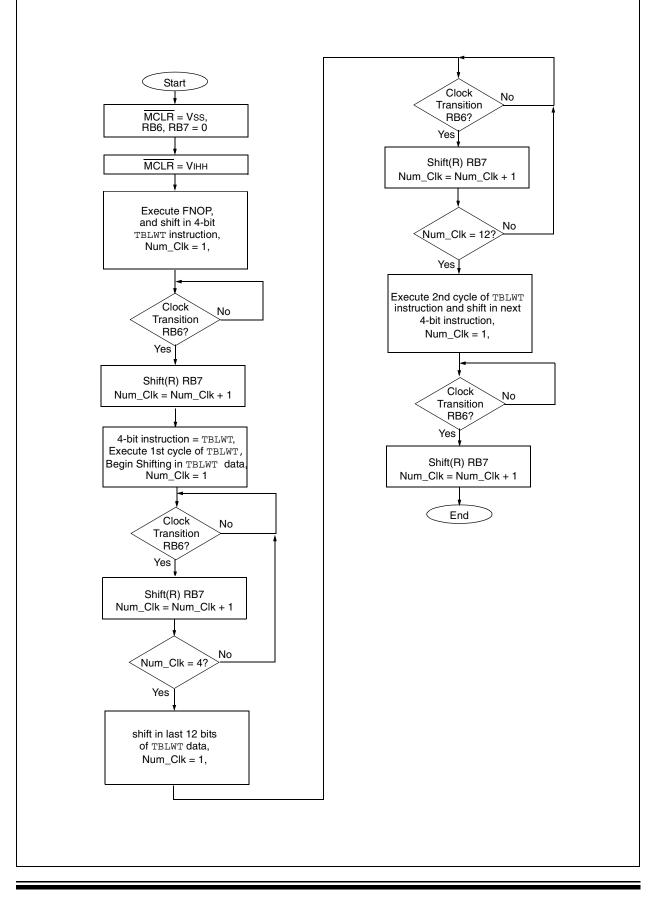

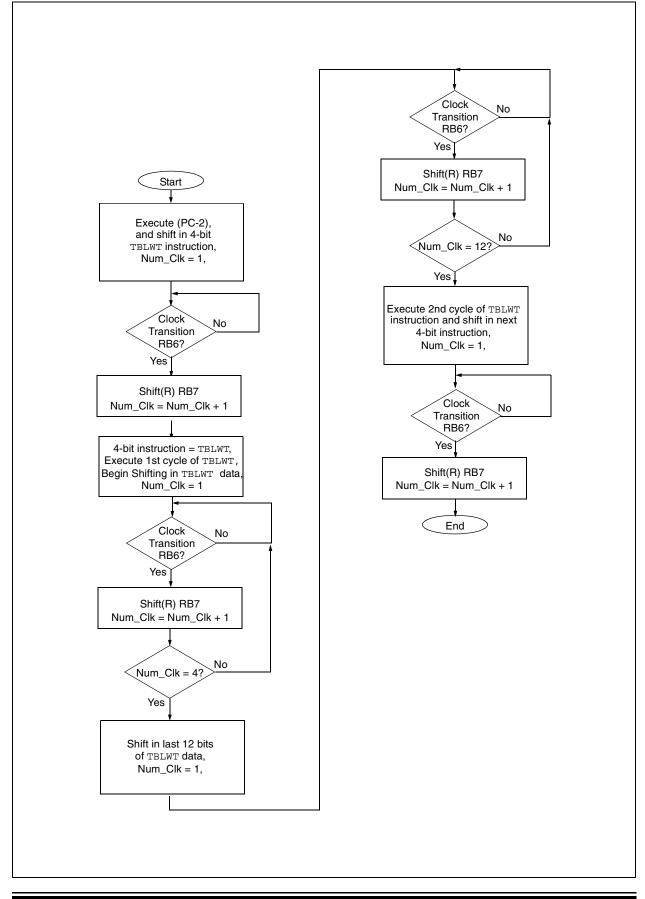

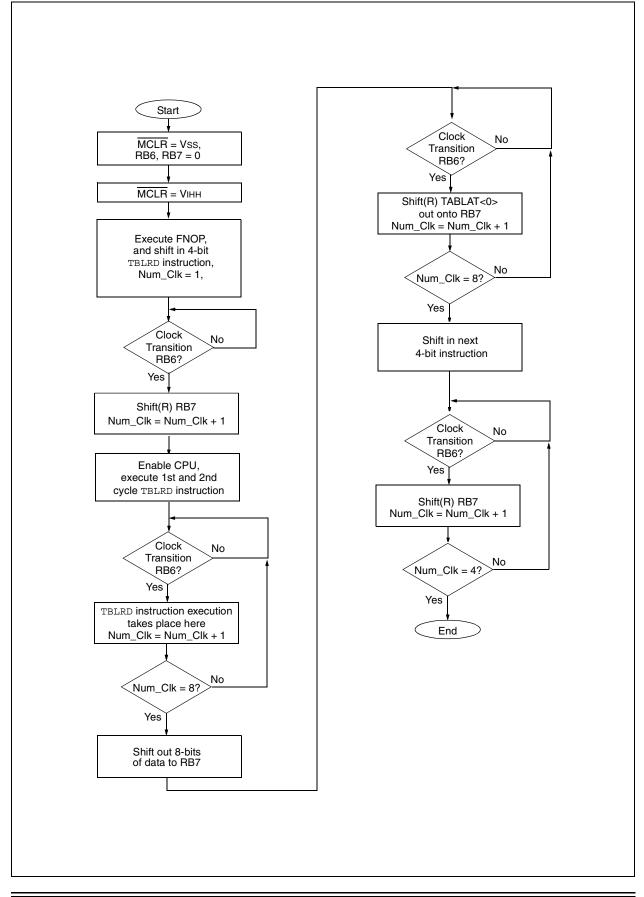

#### Implementation

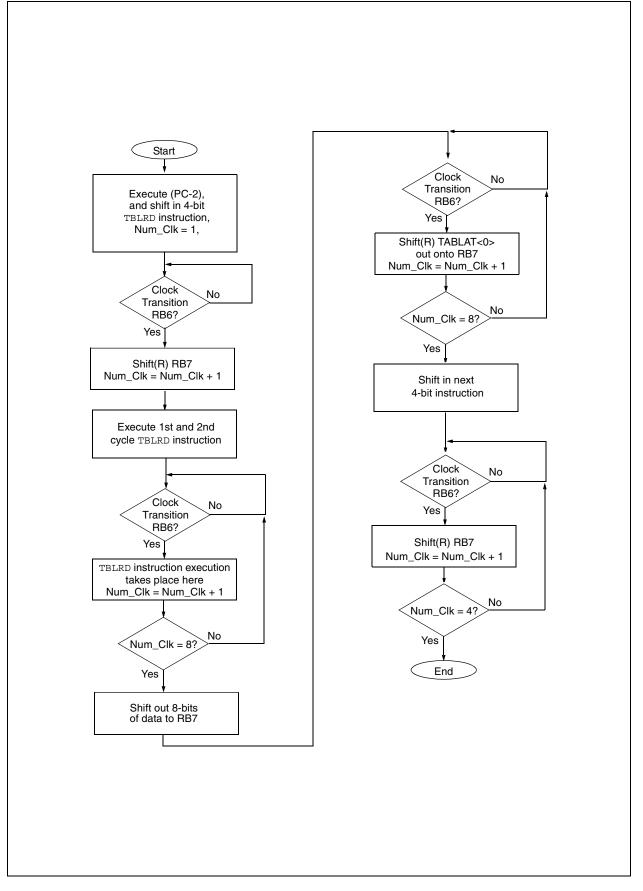

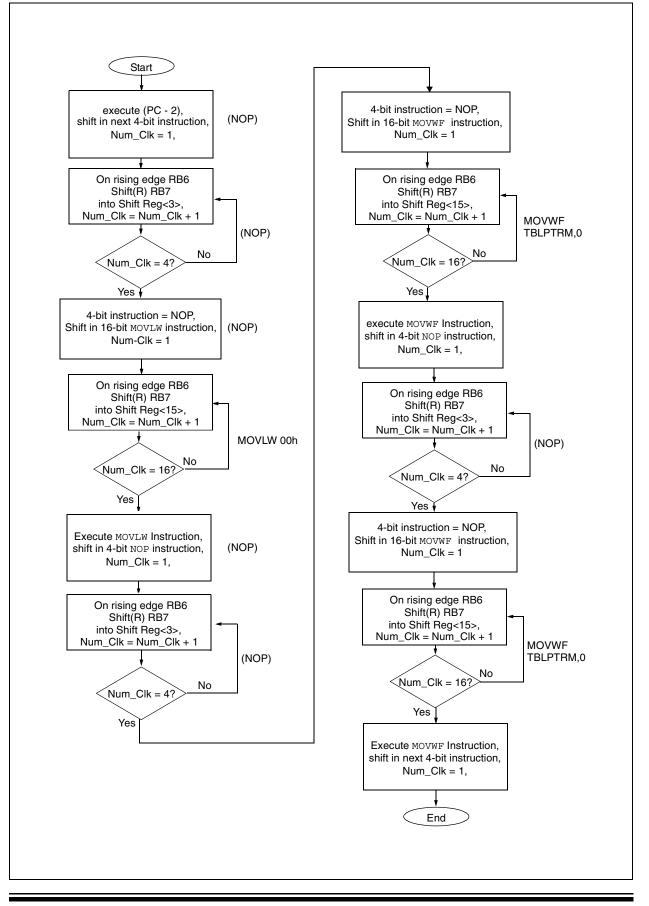

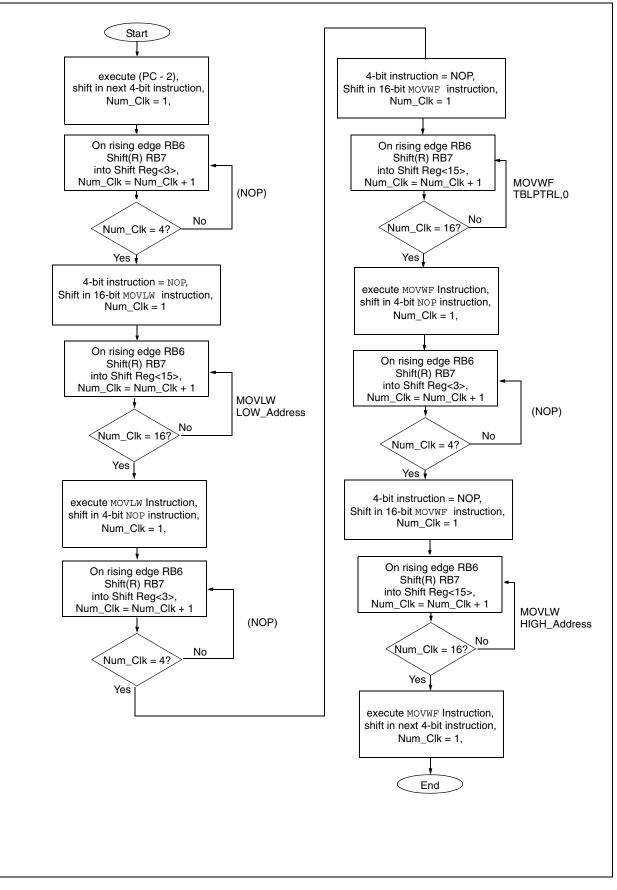

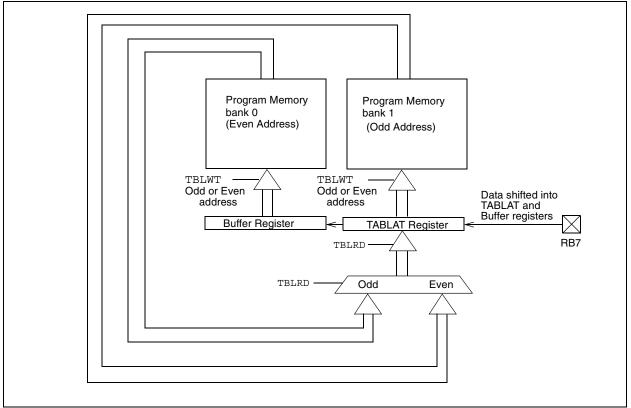

The PIC17CXXX devices have special instructions, which enables the user to program and read the PIC17CXXX's program memory. The instructions are TABLWT and TLWT which implement the program memory write operation and TABLRD and TLRD which perform the program memory read operation. For more details, please check the *In-Circuit Serial Programming for PIC17CXXX OTP Microcontrollers Specification* (DS30273), PIC17C4X data sheet (DS30412) and PIC17C75X data sheet (DS30264).

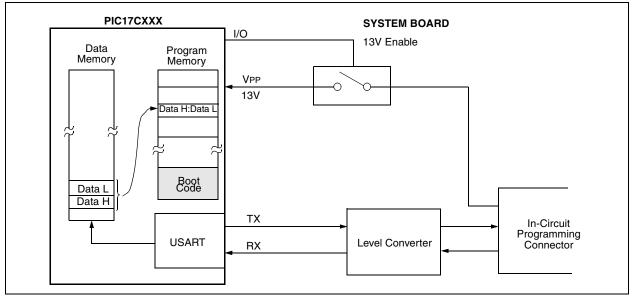

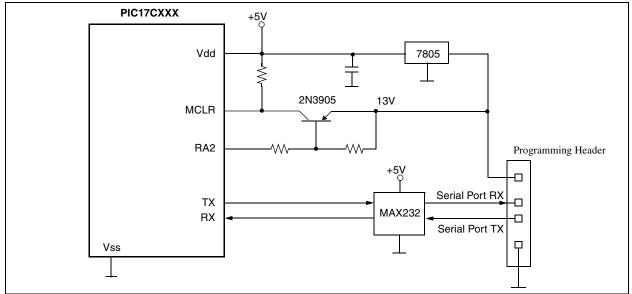

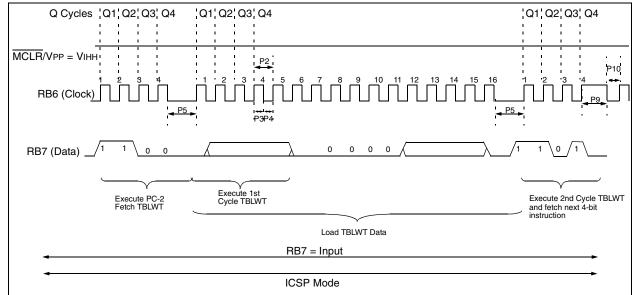

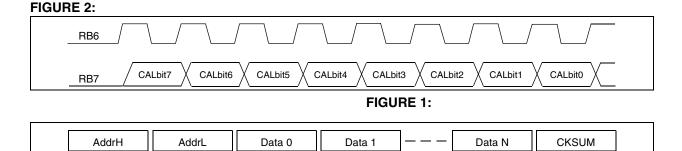

When doing ICSP, the PIC17CXXX runs a boot code, which configures the USART port and receives data serially through the RX line. This data is then programmed at the address specified in the serial data string. A high voltage (about 13V) is required for the EPROM cell to get programmed, and this is usually supplied by the programming header as shown in Figure 2 and Figure 3. The PIC17CXXX's boot code enables and disables the high voltage line using a dedicated I/O line.

### FIGURE 2: PIC17CXXX IN-CIRCUIT SERIAL PROGRAMMING USING TABLE WRITE INSTRUCTIONS

#### FIGURE 3: PIC17CXXX IN-CIRCUIT SERIAL PROGRAMMING SCHEMATIC

#### **ICSP Boot Code**

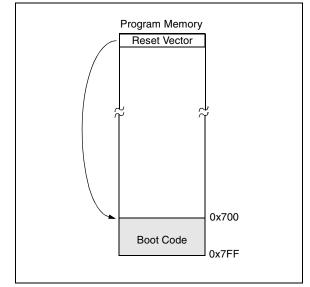

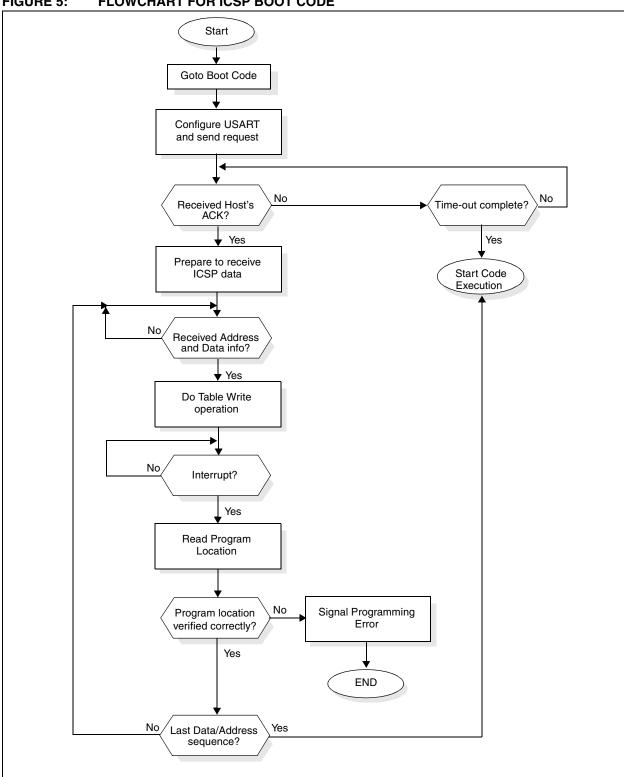

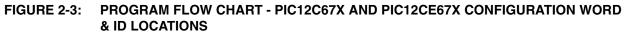

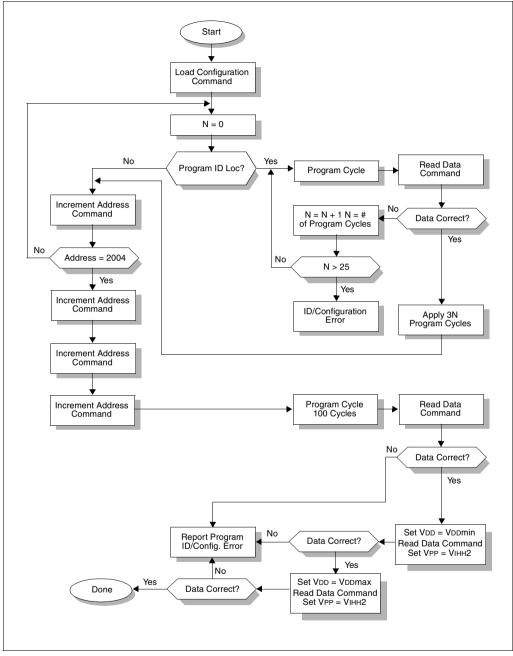

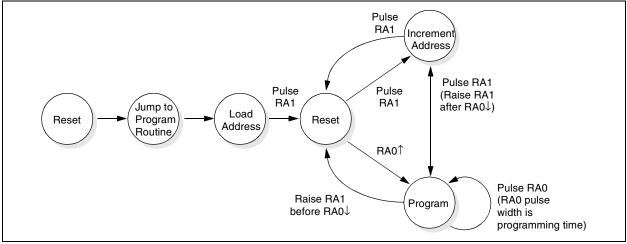

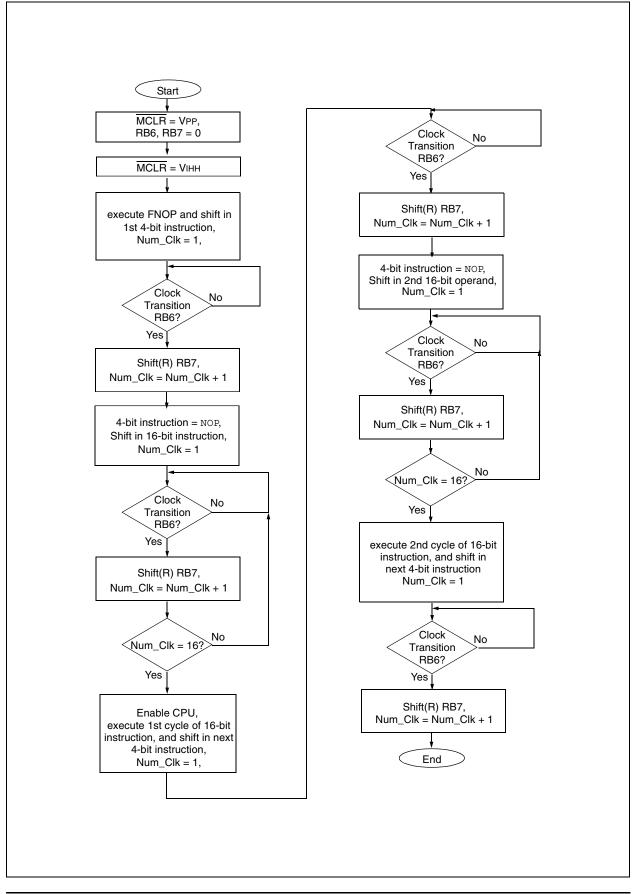

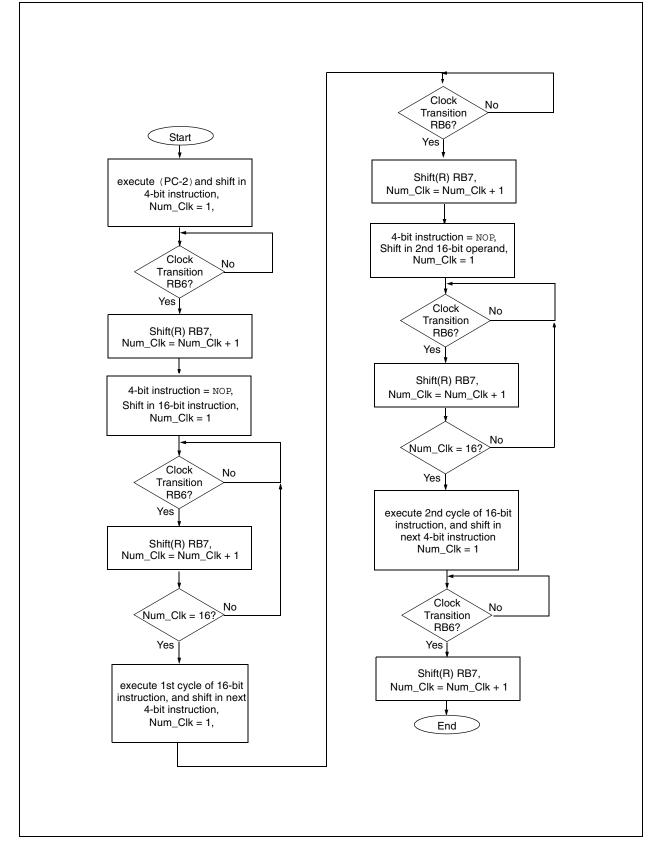

The boot code is normally programmed, into the PIC17CXXX device using a PRO MATE<sup>®</sup> or PICSTART<sup>®</sup> Plus or any third party programmer. As depicted in the flowchart in Figure 5, on power-up, or a reset, the program execution always vectors to the boot code. The boot code is normally located at the bottom of the program memory space e.g. 0x700 for a PIC17C42A (Figure 4).

Several methods could be used to reset the PIC17CXXX when the ICSP header is connected to the system board. The simplest method, as shown in Figure 3, is to derive the system 5V, from the 13V supplied by the ICSP header. It is quite common in manufacturing lines, to have system boards programmed with only the boot code ready and available for testing, calibration or final programming. The ICSP header would thus supply the 13V to the system and this 13V would then be stepped down to supply the 5V required to power the system. Please note that the 13V supply should have enough drive capability to supply power to the system as well as maintain the programming voltage of 13V.

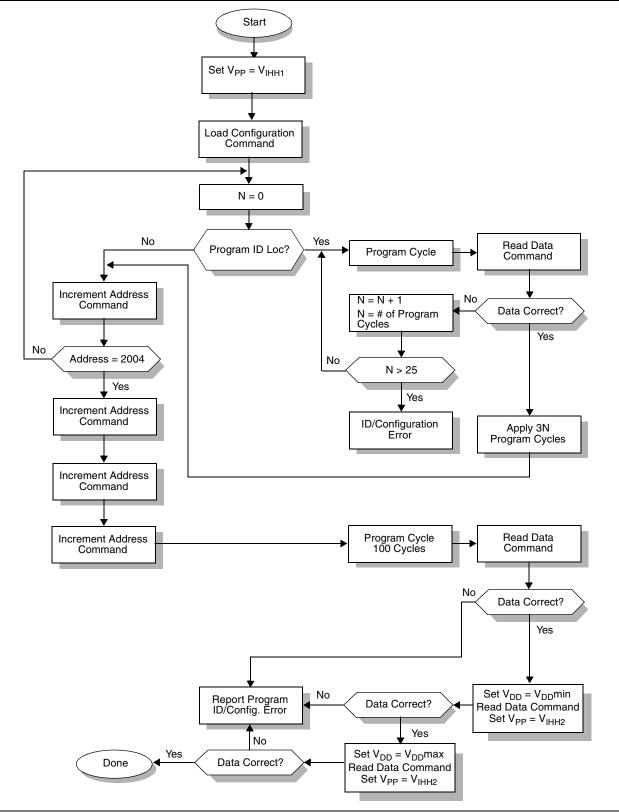

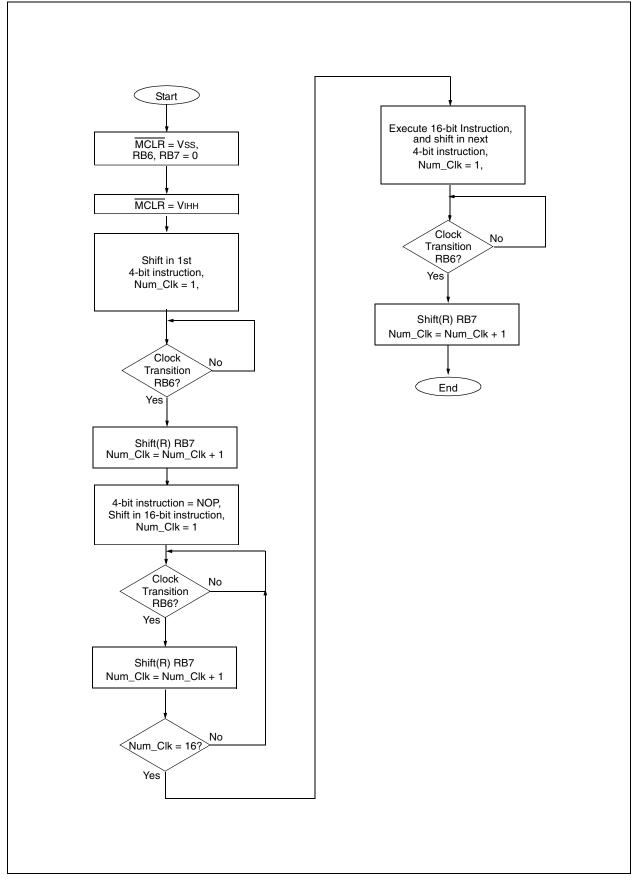

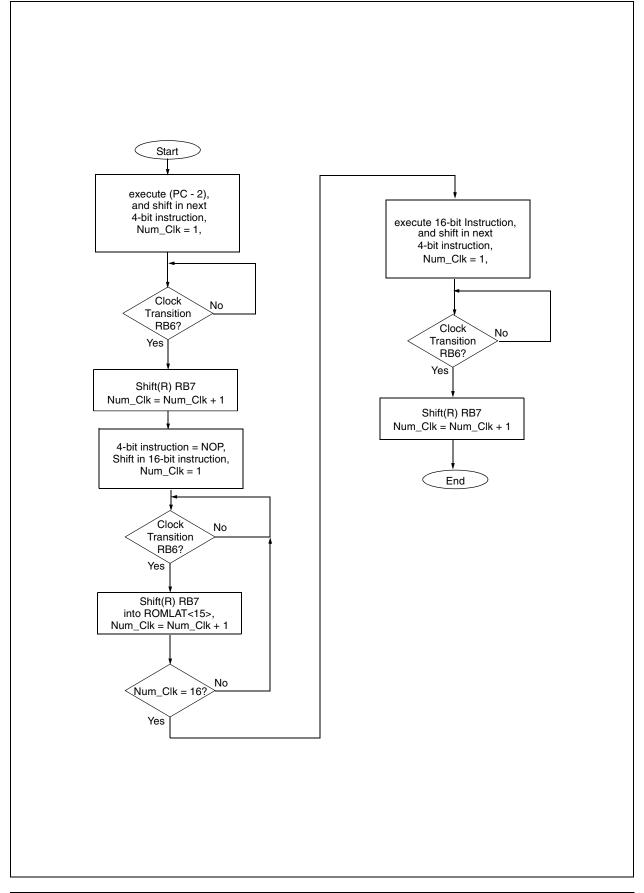

The first action of the boot code (as shown in flowchart Figure 5) is to configure the USART to a known baud rate and transmit a request sequence to the ICSP host system. The host immediately responds with an acknowledgment of this request. The boot code then gets ready to receive ICSP data. The host starts sending the data and address byte sequences to the PIC17CXXX. On receiving the address and data information, the 16-bit address is loaded into the TBLPTR registers and the 16-bit data is loaded into the TABLAT registers. The RA2 pin is driven low to enable 13V at MCLR. The PIC17CXXX device then executes a table write instruction. This instruction in turn causes a long write operation, which disables further code execution. Code execution is resumed when an internal

interrupt occurs. This delay ensures that the programming pulse width of 1 ms (max.) is met. Once a location is written, RA2 is driven high to disable further writes and a verify operation is done using the Table read instruction. If the result is good, an acknowledge is sent to the host. This process is repeated till all desired locations are programmed.

In normal operation, when the ICSP header is not connected, the boot code would still execute and the PIC17CXXX would send out a request to the host. However it would not get a response from the host, so it would abort the boot code and start normal code execution.

#### FIGURE 4: BOOT CODE EXAMPLE FOR PIC17C42A

#### USING THE ICSP FEATURE ON PIC17CXXX OTP DEVICES

The ICSP feature is a very powerful tool when used in conjunction with OTP devices.

#### Saving Calibration Information Using ICSP

One key use of ICSP is to store calibration constants or parameters in program memory. It is quite common to interface a PIC17CXXX device to a sensor. Accurate, pre-calibrated sensors can be used, but they are more expensive and have long lead times. Uncalibrated sensors on the other hand are inexpensive and readily available. The only caveat is that these sensors have to be calibrated in the application. Once the calibration constants have been determined, they would be unique to a given system, so they have to be saved in program memory. These calibration parameters/constants can then be retrieved later during program execution and used to improve the accuracy of low cost un-calibrated sensors. ICSP thus offers a cost reduction path for the end user in the application.

## Saving Field Calibration Information Using ICSP

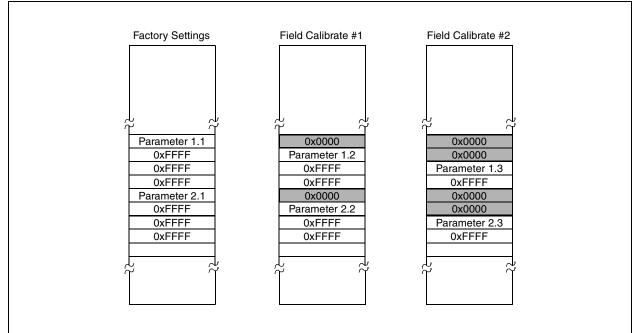

Sensors typically tend to drift and lose calibration over time and usage. One expensive solution would be to replace the sensor with a new one. A more cost effective solution however, is to re-calibrated the system and save the new calibration parameter/constants into the PIC17CXXX devices using ICSP. The user program however has to take into account certain issues:

- 1. Un-programmed or blank locations have to be reserved at each calibration constant location in order to save new calibration parameters/constants.

- The old calibration parameters/constants are all programmed to 0, so the user program will have to be "intelligent" and differentiate between blank (0xFFFF), zero (0x0000), and programmed locations.

Figure 6 shows how this can be achieved.

## Programming Unique Serial Numbers Using ICSP

There are applications where each system needs to have a unique and sometimes random serial number. Example: security devices. One common solution is to have a set of DIP switches which are then set to a unique value during final test. A more cost effective solution however would be to program unique serial numbers into the device using ICSP. The user application can thus eliminate the need for DIP switches and subsequently reduce the cost of the system.

#### FIGURE 6: FIELD CALIBRATION USING ICSP

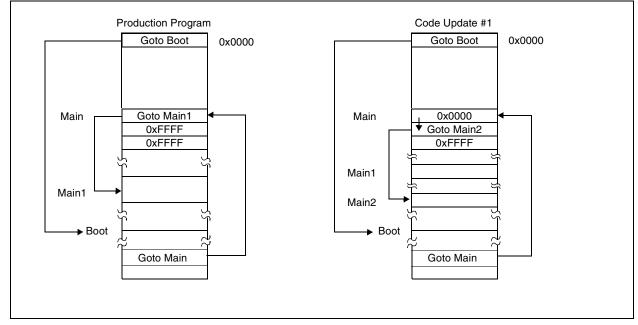

#### Code Updates in the Field Using ICSP

With fast time to market it is not uncommon to see application programs which need to be updated or corrected for either enhancements or minor errors/bugs. If ROM parts were used, updates would be impossible and the product would either become outdated or recalled from the field. A more cost effective solution is to use OTP devices with ICSP and program them in the field with the new updates. Figure 7 shows an example where the user has allowed for one field update to his program.

Here are some of the issues which need to be addressed:

- 1. The user has to reserve sufficient blank memory to fit his updated code.

- 2. At least one blank location needs to be saved at the reset vector as well as for all the interrupts.

- 3. Program all the old "goto" locations (located at the reset vector and the interrupts vectors) to 0 so that these instructions execute as NOPs.

- 4. Program new "goto" locations (at the reset vector and the interrupt vectors) just below the old "goto" locations.

- 5. Finally, program the new updated code in the blank memory space.

#### CONCLUSION

ICSP is a very powerful feature available on the PIC17CXXX devices. It offers tremendous design flexibility to the end user in terms of saving calibration constants and updating code in final production as well as in the field, thus helping the user design a low-cost and fast time-to-market product.

#### FIGURE 7: CODE UPDATES USING ICSP

NOTES:

### How to Implement ICSP<sup>TM</sup> Using PIC16F8X FLASH MCUs

Author: Rodger Richey Microchip Technology Inc.

#### INTRODUCTION

In-Circuit Serial Programming™ (ICSP) with PICmicro<sup>®</sup> FLASH microcontrollers (MCU) is not only a great way to reduce your inventory overhead and timeto-market for your product, but also to easily provide field upgrades of firmware. By assembling your product with a Microchip FLASH-based MCU, you can stock the shelf with one system. When an order has been placed, these units can be programmed with the latest revision of firmware, tested, and shipped in a very short time. This type of manufacturing system can also facilitate quick turnarounds on custom orders for your product. You don't have to worry about scrapped inventory because of the FLASH-based program memory. This gives you the advantage of upgrading the firmware at any time to fix those "features" that pop up from time to time.

#### HOW DOES ICSP WORK?

Now that ICSP appeals to you, what steps do you take to implement it in your application? There are three main components of an ICSP system.

These are the: Application Circuit, Programmer and Programming Environment.

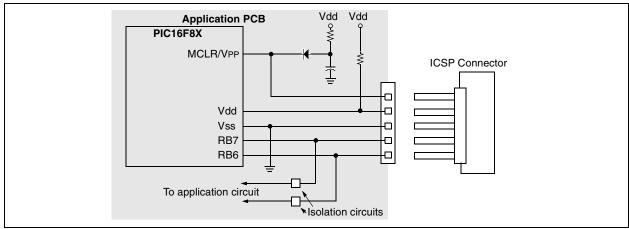

#### FIGURE 1: TYPICAL APPLICATION CIRCUIT

#### **Application Circuit**

The application circuit must be designed to allow all the programming signals to be directly connected to the PICmicro MCUs. Figure 1 shows a typical circuit that is a starting point for when designing with ICSP. The application must compensate for the following issues:

- 1. Isolation of the MCLR/VPP pin from the rest of the circuit.

- Isolation of pins RB6 and RB7 from the rest of the circuit.

- 3. Capacitance on each of the VDD, MCLR/VPP, RB6, and RB7 pins.

- 4. Minimum and maximum operating voltage for  $V_{\text{DD}}.$

- 5. PICmicro Oscillator.

- 6. Interface to the programmer.

The MCLR/VPP pin is normally connected to an RC circuit. The pull-up resistor is tied to VDD and a capacitor is tied to ground. This circuit can affect the operation of ICSP depending on the size of the capacitor. It is, therefore, recommended that the circuit in Figure 1 be used when an RC is connected to MCLR/VPP. The diode should be a Schottky-type device. Another issue with MCLR/VPP is that when the PICmicro MCU device is programmed, this pin is driven to approximately 13V and also to ground. Therefore, the application circuit must be isolated from this voltage provided by the programmer.

PICmicro, PRO MATE, and PICSTART are registered trademarks of Microchip Technology Inc. In-Circuit Serial Programming and ICSP are trademarks of Microchip Technology Inc.

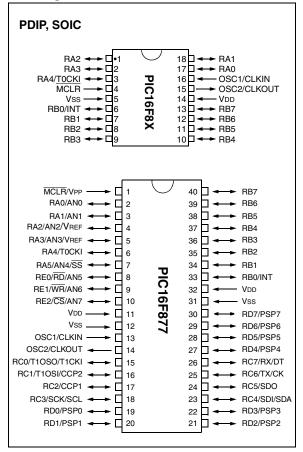

Pins RB6 and RB7 are used by the PICmicro MCU for serial programming. RB6 is the clock line and RB7 is the data line. RB6 is driven by the programmer. RB7 is a bidirectional pin that is driven by the programmer when programming, and driven by the PICmicro MCU when verifying. These pins must be isolated from the rest of the application circuit so as not to affect the signals during programming. You must take into consideration the output impedance of the programmer when isolating RB6 and RB7 from the rest of the circuit. This isolation circuit must account for RB6 being an input on the PICmicro MCU and for RB7 being bidirectional (can be driven by both the PICmicro MCU and the programmer). For instance, PRO MATE® II has an output impedance of 1k3/4. If the design permits, these pins should not be used by the application. This is not the case with most applications so it is recommended that the designer evaluate whether these signals need to be buffered. As a designer, you must consider what type of circuitry is connected to RB6 and RB7 and then make a decision on how to isolate these pins. Figure 1 does not show any circuitry to isolate RB6 and RB7 on the application circuit because this is very application dependent.

The total capacitance on the programming pins affects the rise rates of these signals as they are driven out of the programmer. Typical circuits use several hundred microfarads of capacitance on VDD which helps to dampen noise and ripple. However, this capacitance requires a fairly strong driver in the programmer to meet the rise rate timings for VDD. Most programmers are designed to simply program the PICmicro MCU itself and don't have strong enough drivers to power the application circuit. One solution is to use a driver board between the programmer and the application circuit. The driver board requires a separate power supply that is capable of driving the VPP and VDD pins with the correct rise rates and should also provide enough current to power the application circuit. RB6 and RB7 are not buffered on this schematic but may require buffering depending upon the application. A sample driver board schematic is shown in Appendix A.

**Note:** The driver board design MUST be tested in the user's application to determine the effects of the application circuit on the programming signals timing. Changes may be required if the application places a significant load on Vdd, VPP, RB6 or RB7.

The Microchip programming specification states that the device should be programmed at 5V. Special considerations must be made if your application circuit operates at 3V only. These considerations may include totally isolating the PICmicro MCU during programming. The other issue is that the device must be verified at the minimum and maximum voltages at which the application circuit will be operating. For instance, a battery operated system may operate from three 1.5V cells giving an operating voltage range of 2.7V to 4.5V. The programmer must program the device at 5V and must verify the program memory contents at both 2.7V and 4.5V to ensure that proper programming margins have been achieved. This ensures the PICmicro MCU option over the voltage range of the system.

This final issue deals with the oscillator circuit on the application board. The voltage on MCLR/VPP must rise to the specified program mode entry voltage before the device executes any code. The crystal modes available on the PICmicro MCU are not affected by this issue because the Oscillator Start-up Timer waits for 1024 oscillations before any code is executed. However, RC oscillators do not require any startup time and, therefore, the Oscillator Startup Timer is not used. The programmer must drive MCLR/VPP to the program mode entry voltage before the RC oscillator toggles four times. If the RC oscillator toggles four or more times, the program counter will be incremented to some value X. Now when the device enters programming mode, the program counter will not be zero and the programmer will start programming your code at an offset of X. There are several alternatives that can compensate for a slow rise rate on MCLR/VPP. The first method would be to not populate the R, program the device, and then insert the R. The other method would be to have the programming interface drive the OSC1 pin of the PICmicro MCU to ground while programming. This will prevent any oscillations from occurring during programming.

Now all that is left is how to connect the application circuit to the programmer. This depends a lot on the programming environment and will be discussed in that section.

#### Programmer

The second consideration is the programmer. PIC16F8X MCUs only use serial programming and therefore all programmers supporting these devices will support ICSP. One issue with the programmer is the drive capability. As discussed before, it must be able to provide the specified rise rates on the ICSP signals and also provide enough current to power the application circuit. Appendix A shows an example driver board. This driver schematic does not show any buffer circuitry for RB6 and RB7. It is recommended that an evaluation be performed to determine if buffering is required. Another issue with the programmer is what VDD levels are used to verify the memory contents of the PICmicro MCU. For instance, the PRO MATE II verifies program memory at the minimum and maximum VDD levels for the specified device and is therefore considered a production quality programmer. On the other hand, the PICSTART<sup>®</sup> Plus only verifies at 5V and is for prototyping use only. The Microchip programming specifications state that the program memory contents should be verified at both the minimum and maximum VDD levels that the application circuit will be operating. This implies that the application circuit must be able to handle the varying VDD voltages.

There are also several third party programmers that are available. You should select a programmer based on the features it has and how it fits into your programming environment. The *Microchip Development Systems Ordering Guide* (DS30177) provides detailed information on all our development tools. The *Microchip Third Party Guide* (DS00104) provides information on all of our third party tool developers. Please consult these two references when selecting a programmer. Many options exist including serial or parallel PC host connection, stand-alone operation, and single or gang programmers. Some of the third party developers include Advanced Transdata Corporation, BP Microsystems, Data I/O, Emulation Technology and Logical Devices.

#### **Programming Environment**

The programming environment will affect the type of programmer used, the programmer cable length, and the application circuit interface. Some programmers are well suited for a manual assembly line while others are desirable for an automated assembly line. You may want to choose a gang programmer to program multiple systems at a time.

The physical distance between the programmer and the application circuit affects the load capacitance on each of the programming signals. This will directly affect the drive strength needed to provide the correct signal rise rates and current. This programming cable must also be as short as possible and properly terminated and shielded or the programming signals may be corrupted by ringing or noise.

Finally, the application circuit interface to the programmer depends on the size constraints of the application circuit itself and the assembly line. A simple header can be used to interface the application circuit to the programmer. This might be more desirable for a manual assembly line where a technician plugs the programmer cable into the board. A different method is the use of spring loaded test pins (commonly referred to as pogo pins). The application circuit has pads on the board for each of the programming signals. Then there is a fixture that has pogo pins in the same configuration as the pads on the board. The application circuit or fixture is moved into position such that the pogo pins come into contact with the board. This method might be more suitable for an automated assembly line.

After taking into consideration the issues with the application circuit, the programmer, and the programming environment, anyone can build a high quality, reliable manufacturing line based on ICSP.

#### **Other Benefits**

ICSP provides other benefits, such as calibration and serialization. If program memory permits, it would be cheaper and more reliable to store calibration constants in program memory instead of using an external serial EEPROM. For example, your system has a thermistor which can vary from one system to another. Storing some calibration information in a table format allows the microcontroller to compensate in software for external component tolerances. System cost can be reduced without affecting the required performance of the system by using software calibration techniques. But how does this relate to ICSP? The PICmicro MCU has already been programmed with firmware that performs a calibration cycle. The calibration data is transferred to a calibration fixture. When all calibration data has been transferred, the fixture places the PICmicro MCU in programming mode and programs the PICmicro MCU with the calibration data. Application note AN656, In-Circuit Serial Programming of Calibration Parameters Using a PICmicro Microcontroller, shows exactly how to implement this type of calibration data programming.

The other benefit of ICSP is serialization. Each individual system can be programmed with a unique or random serial number. One such application of a unique serial number would be for security systems. A typical system might use DIP switches to set the serial number. Instead, this number can be burned into program memory thus reducing the overall system cost and lowering the risk of tampering.

#### Field Programming of FLASH PICmicro MCUs

With the ISP interface circuitry already in place, these FLASH-based PICmicro MCUs can be easily reprogrammed in the field. These FLASH devices allow you to reprogram them even if they are code protected. A portable ISP programming station might consist of a laptop computer and programmer. The technician plugs the ISP interface cable into the application circuit and downloads the new firmware into the PICmicro MCU. The next thing you know the system is up and running without those annoying "bugs". Another instance would be that you want to add an additional feature to your system. All of your current inventory can be converted to the new firmware and field upgrades can be performed to bring your installed base of systems up to the latest revision of firmware.

#### CONCLUSION

Microchip Technology Inc. is committed to supporting your ICSP needs by providing you with our many years of experience and expertise in developing ICSP solutions. Anyone can create a reliable ICSP programming station by coupling our background with some forethought to the circuit design and programmer selection issues previously mentioned. Your local Microchip representative is available to answer any questions you have about the requirements for ICSP.

#### APPENDIX A: SAMPLE DRIVER BOARD SCHEMATIC

# SECTION 3 PROGRAMMING SPECIFICATIONS

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC12C5XX OTP MCUs                | 3-1   |

|---------------------------------------------------------------------|-------|

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC12C67X AND PIC12CE67X OTP MCUs | 3-15  |

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC14000 OTP MCUs                 | 3-27  |

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC16C55X OTP MCUs                | 3-39  |

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC16C6XX/7XX/9XX OTP MCUsS       | 3-51  |

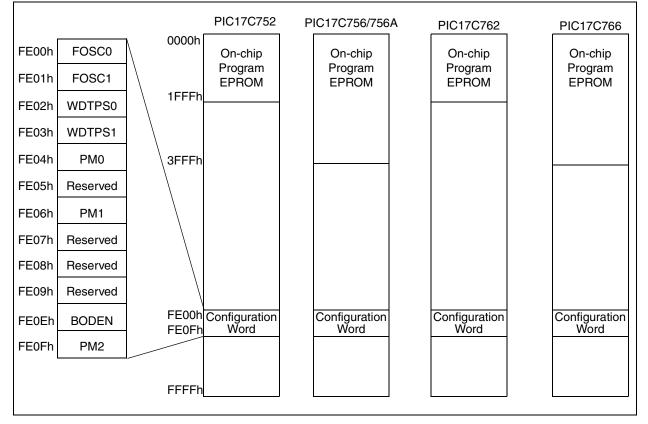

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC17C7XX OTP MCUs                | 3-71  |

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC18CXXX OTP MCUs                | 3-97  |

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC16F62X FLASH MCUs              | 3-135 |

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC16F8X FLASH MCUs               | 3-149 |

| IN-CIRCUIT SERIAL PROGRAMMING FOR PIC16F8XX FLASH MCUs              | 3-165 |

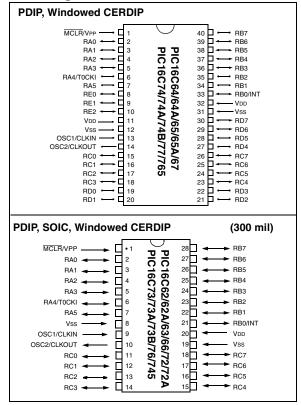

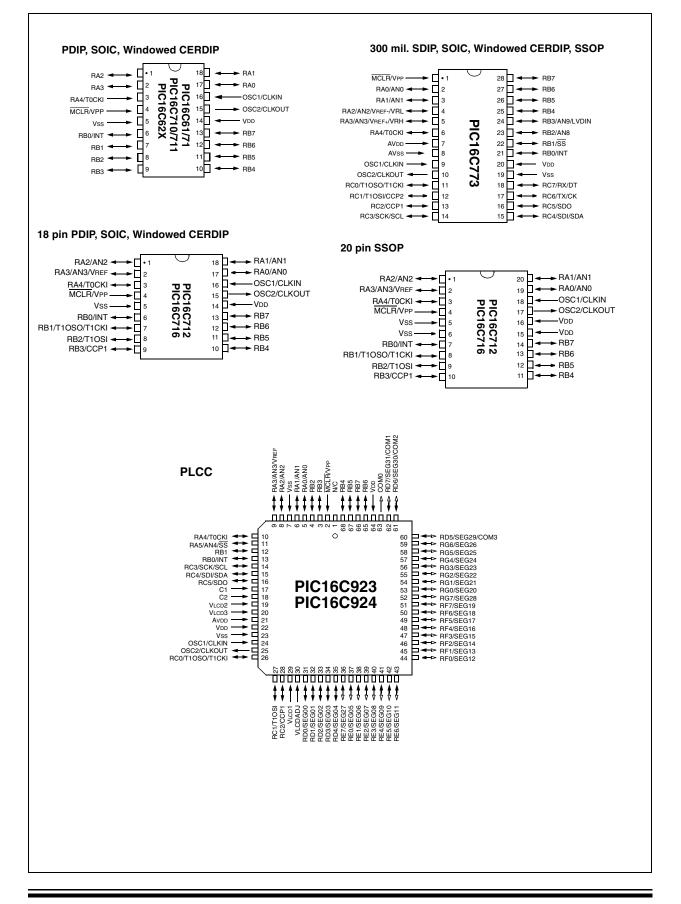

# PIC12C5XX

### **In-Circuit Serial Programming for PIC12C5XX OTP MCUs**

# This document includes the programming specifications for the following devices:

- PIC12C508 PIC12C508A PIC12CE518

- PIC12C509 PIC12C509A PIC12CE519

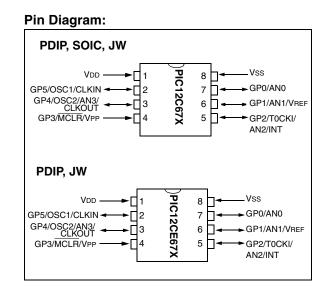

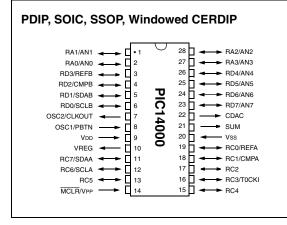

#### 1.0 PROGRAMMING THE PIC12C5XX

The PIC12C5XX can be programmed using a serial method. Due to this serial programming, the PIC12C5XX can be programmed while in the user's system increasing design flexibility. This programming specification applies to PIC12C5XX devices in all packages.

#### 1.1 Hardware Requirements

The PIC12C5XX requires two programmable power supplies, one for VDD (2.0V to 6.5V recommended) and one for VPP (12V to 14V). Both supplies should have a minimum resolution of 0.25V.

#### 1.2 <u>Programming Mode</u>

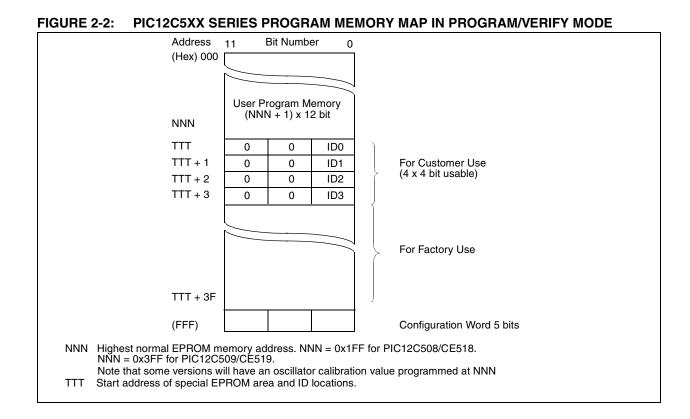

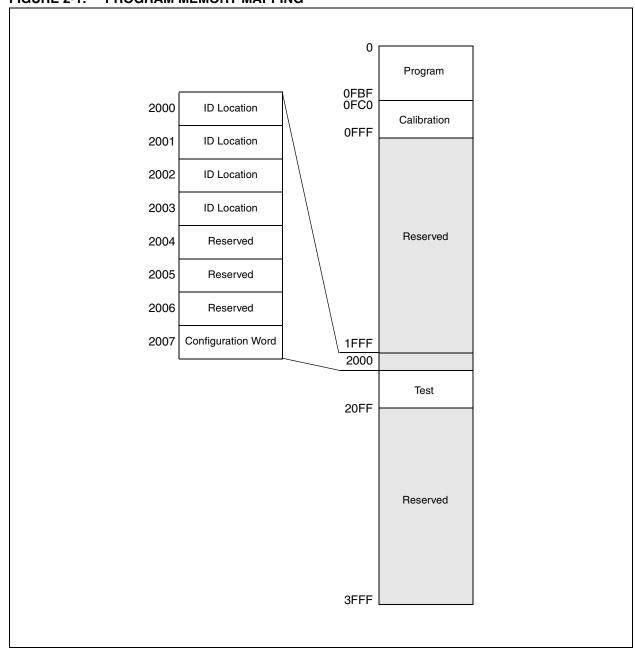

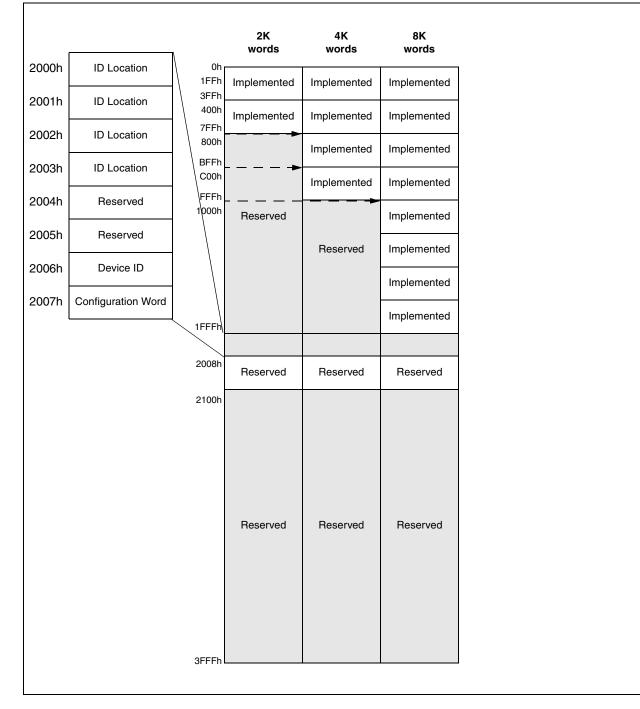

The programming mode for the PIC12C5XX allows programming of user program memory, special locations used for ID, and the configuration word for the PIC12C5XX.

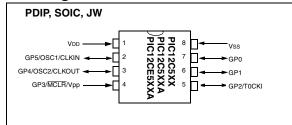

#### **Pin Diagram**

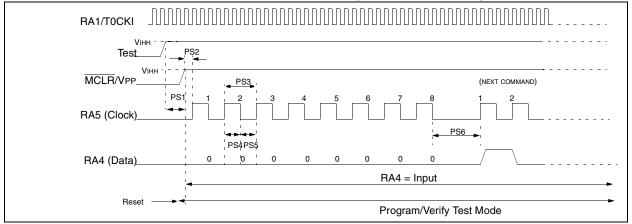

#### 2.0 PROGRAM MODE ENTRY

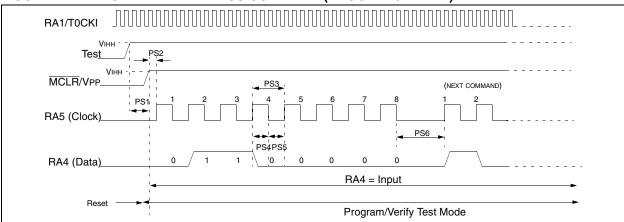

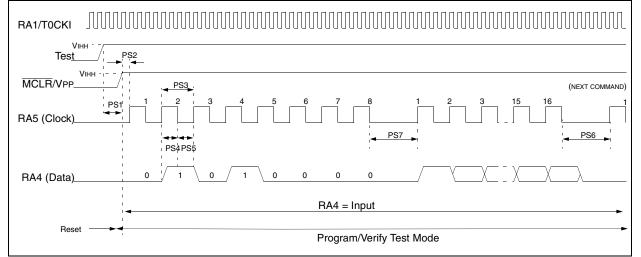

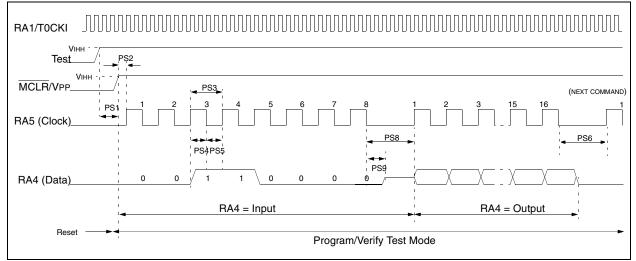

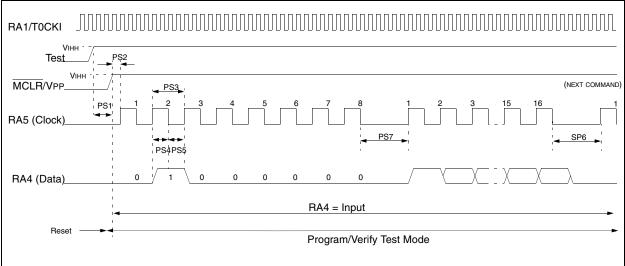

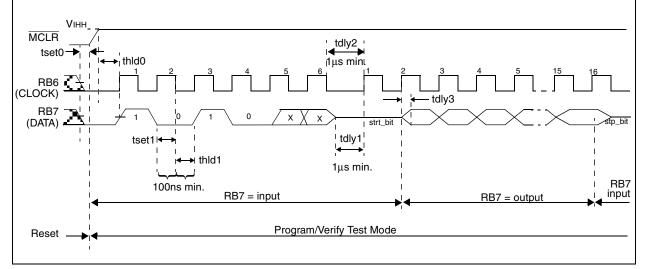

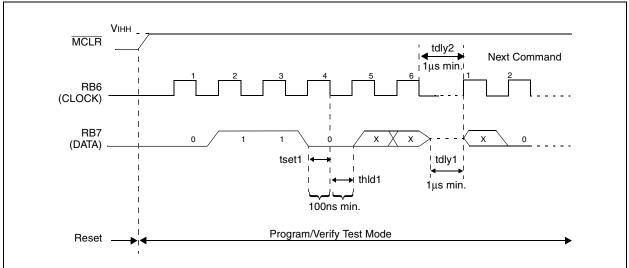

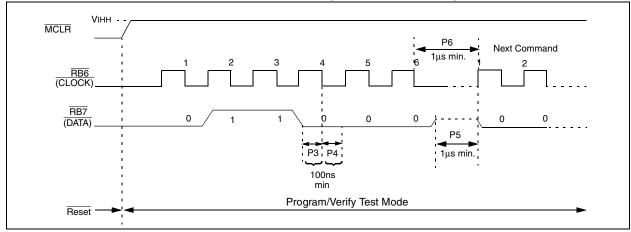

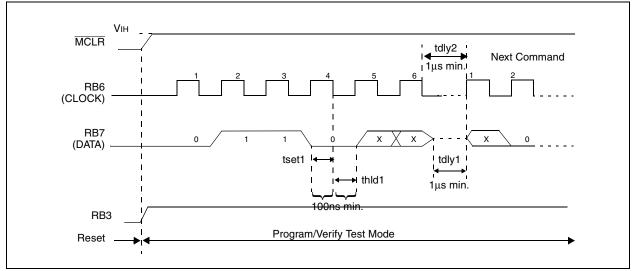

The program/verify test mode is entered by holding pins DB0 and DB1 low while raising  $\overline{\text{MCLR}}$  pin from VIL to VIHH. Once in this test mode the user program memory and the test program memory can be accessed and programmed in a serial fashion. The first selected memory location is the fuses. **GP0 and GP1 are Schmitt trigger inputs in this mode**.

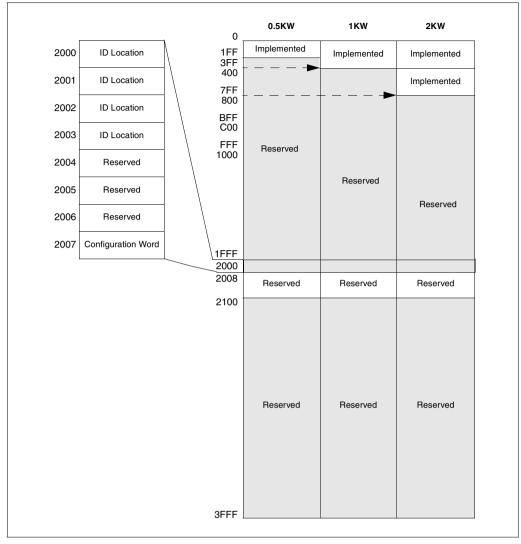

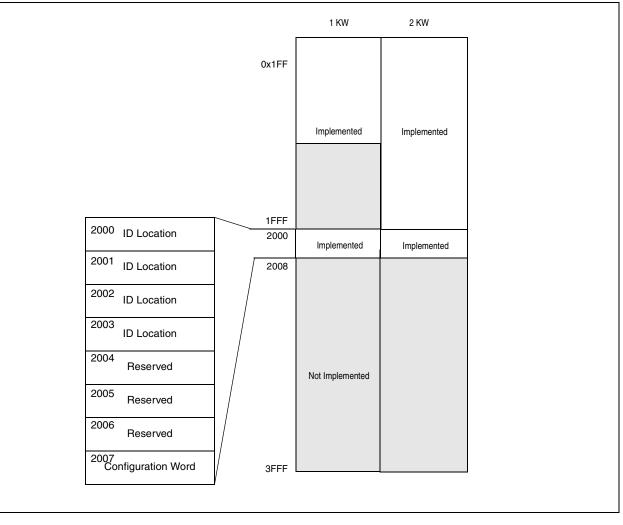

Incrementing the PC once (using the increment address command) selects location 0x000 of the regular program memory. Afterwards all other memory locations from 0x001-01FF (PIC12C508/CE518), 0x001-03FF (PIC12C509/CE519) can be addressed by incrementing the PC.

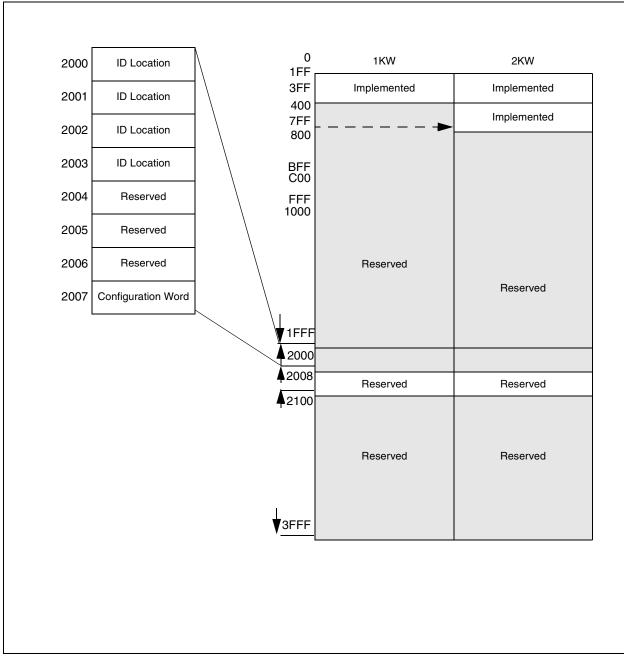

If the program counter has reached the last user program location and is incremented again, the on-chip special EPROM area will be addressed. (See Figure 2-2 to determine where the special EPROM area is located for the various PIC12C5XX devices).

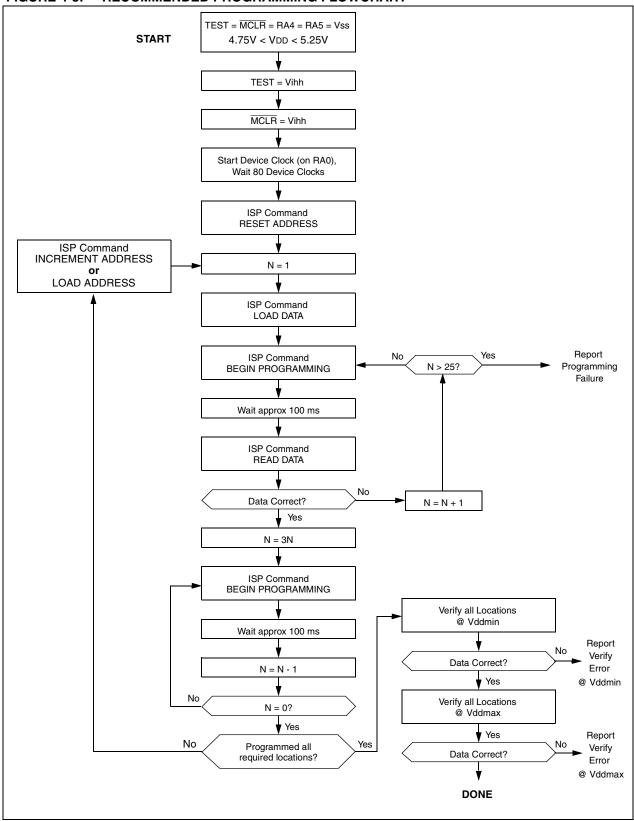

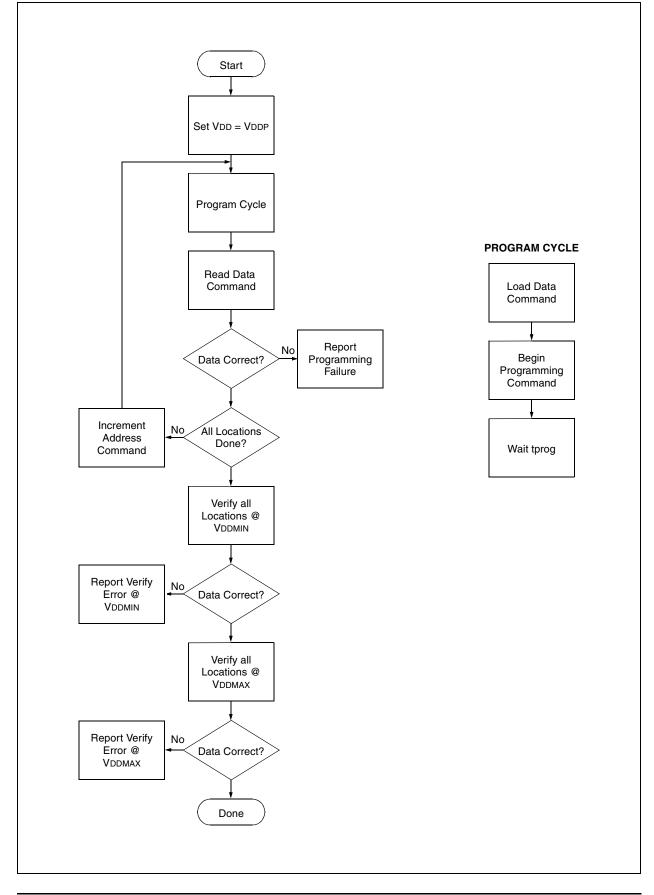

#### 2.1 Programming Method

The programming technique is described in the following section. It is designed to guarantee good programming margins. It does, however, require a variable power supply for Vcc.

#### 2.1.1 PROGRAMMING METHOD DETAILS

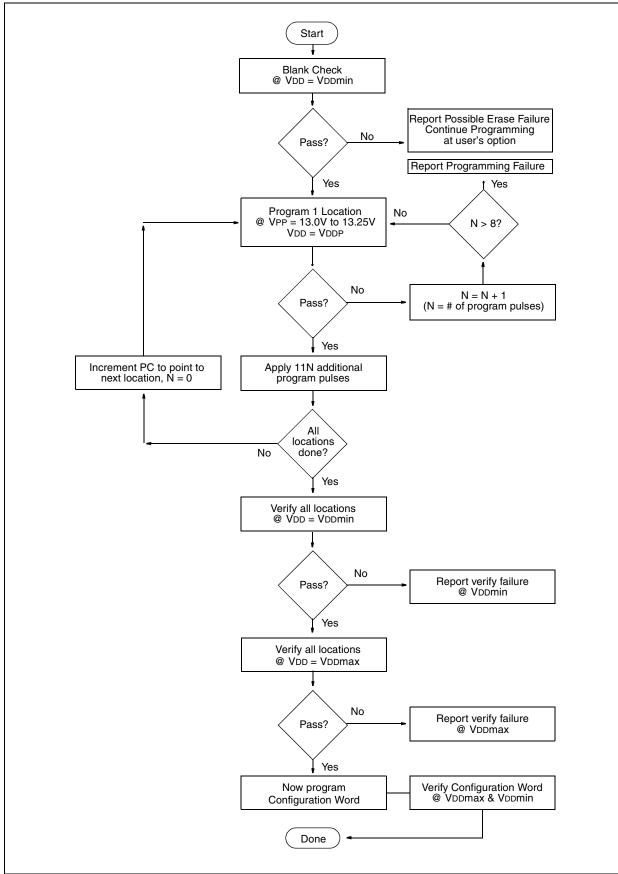

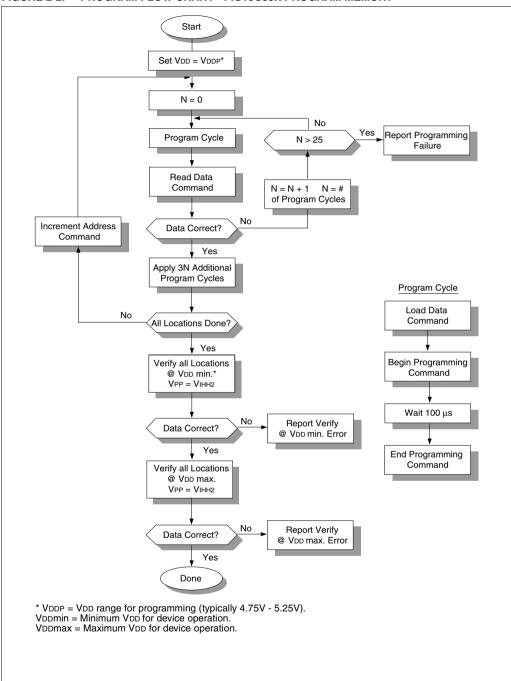

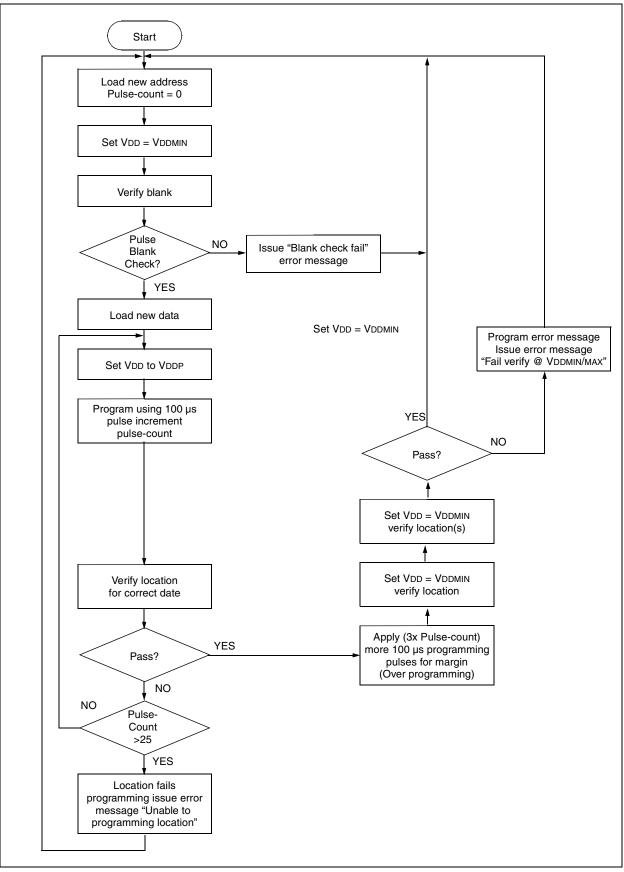

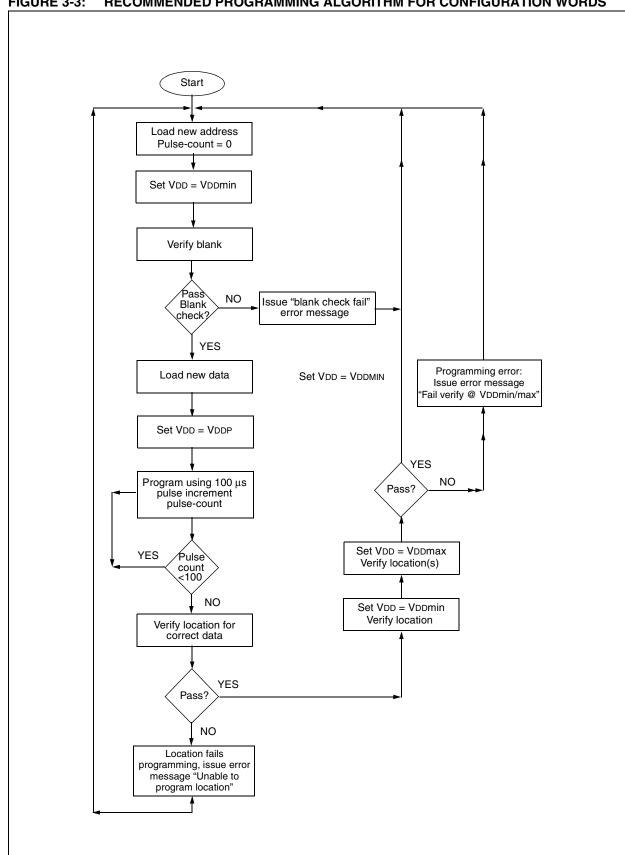

Essentially, this technique includes the following steps:

- 1. Perform blank check at VDD = VDDmin. Report failure. The device may not be properly erased.

- Program location with pulses and verify after each pulse at VDD = VDDP: where VDDP = VDD range required during programming (4.5V - 5.5V).

- a) Programming condition:

- VPP = 13.0V to 13.25V

- VDD = VDDP = 4.5V to 5.5V

VPP must be  $\geq$  VDD + 7.25V to keep "programming mode" active.

b) Verify condition:

VDD = VDDP

$VPP \ge VDD + 7.5V$  but not to exceed 13.25V

If location fails to program after "N" pulses, (suggested maximum program pulses of 8) then report error as a programming failure.

| Note: | Device must be verified at minimum and  |  |

|-------|-----------------------------------------|--|

|       | maximum specified operating voltages as |  |

|       | specified in the data sheet.            |  |

- 3. Once location passes "Step 2", apply 11X over programming, i.e., apply 11 times the number of pulses that were required to program the location. This will guarantee a solid programming margin. The over programming should be made "software programmable" for easy updates.

- 4. Program all locations.

- 5. Verify all locations (using speed verify mode) at VDD = VDDmin

- 6. Verify all locations at VDD = VDDmax

VDDmin is the minimum operating voltage spec. for the part. VDDmax is the maximum operating voltage spec. for the part.

#### 2.1.2 SYSTEM REQUIREMENTS

Clearly, to implement this technique, the most stringent requirements will be that of the power supplies:

**VPP:** VPP can be a fixed 13.0V to 13.25V supply. It must not exceed 14.0V to avoid damage to the pin and should be current limited to approximately 100mA.

**VDD:** 2.0V to 6.5V with 0.25V granularity. Since this method calls for verification at different VDD values, a programmable VDD power supply is needed.

#### Current Requirement: 40mA maximum

Microchip may release devices in the future with different VDD ranges which make it necessary to have a programmable VDD.

It is important to verify an EPROM at the voltages specified in this method to remain consistent with Microchip's test screening. For example, a PIC12C5XX specified for 4.5V to 5.5V should be tested for proper programming from 4.5V to 5.5V.

Note: Any programmer not meeting the programmable VDD requirement and the verify at VDDmax and VDDmin requirement may only be classified as "prototype" or "development" programmer but not a production programmer.

#### 2.1.3 SOFTWARE REQUIREMENTS

Certain parameters should be programmable (and therefore easily modified) for easy upgrade.

- a) Pulse width

- b) Maximum number of pulses, present limit 8.

- c) Number of over-programming pulses: should be =  $(A \cdot N) + B$ , where N = number of pulses required in regular programming. In our current algorithm A = 11, B = 0.

#### 2.2 Programming Pulse Width

**Program Memory Cells**: When programming one word of EPROM, a programming pulse width (TPW) of 100µs is recommended.

The maximum number of programming attempts should be limited to 8 per word.

After the first successful verify, the same location should be over-programmed with 11X over-programming.

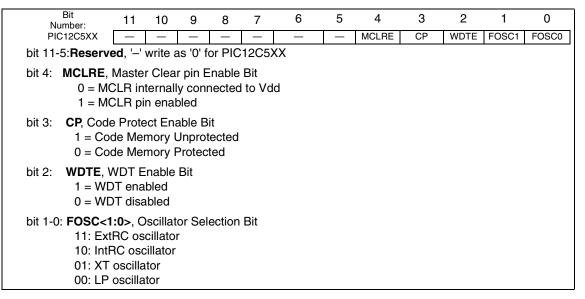

**Configuration Word**: The configuration word for oscillator selection, WDT (watchdog timer) disable and code protection, and MCLR enable, requires a programming pulse width (TPWF) of 10ms. A series of  $100\mu$ s pulses is preferred over a single 10ms pulse.

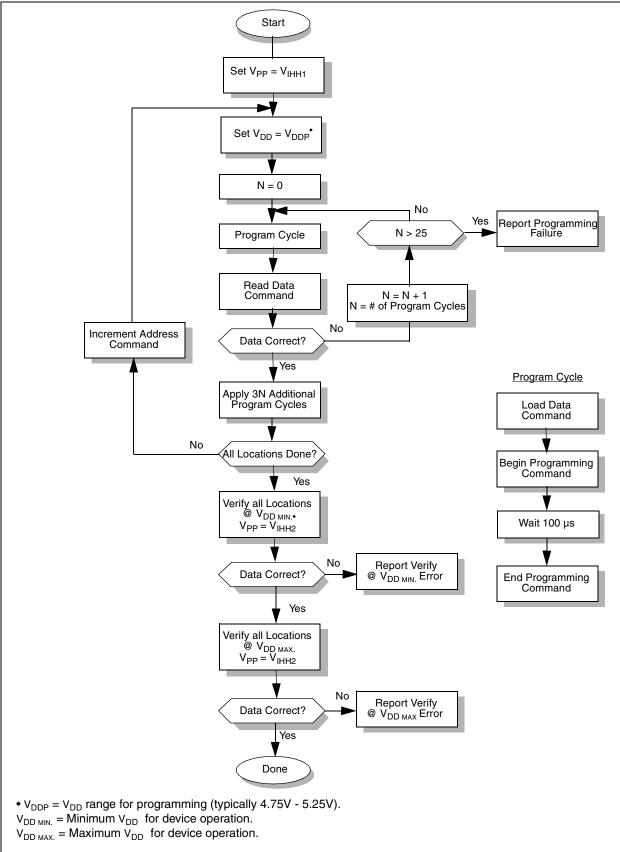

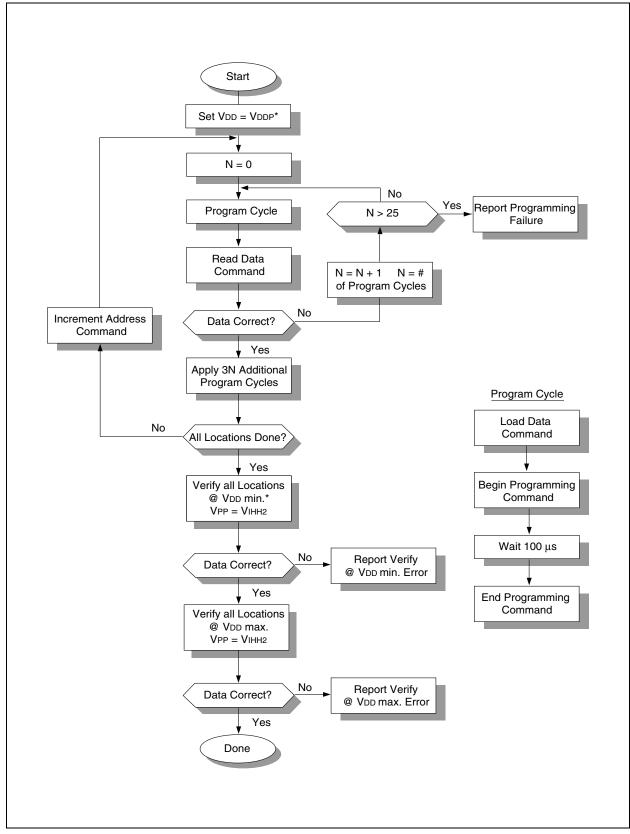

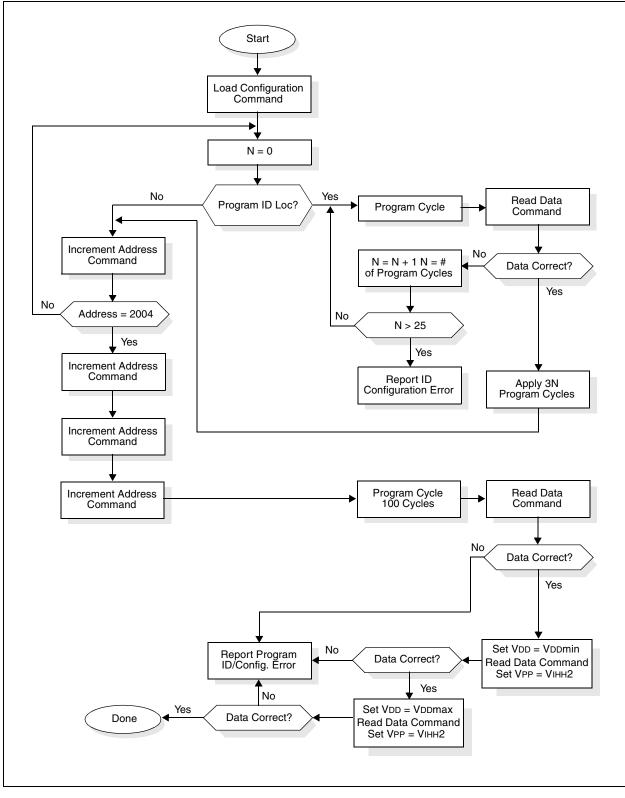

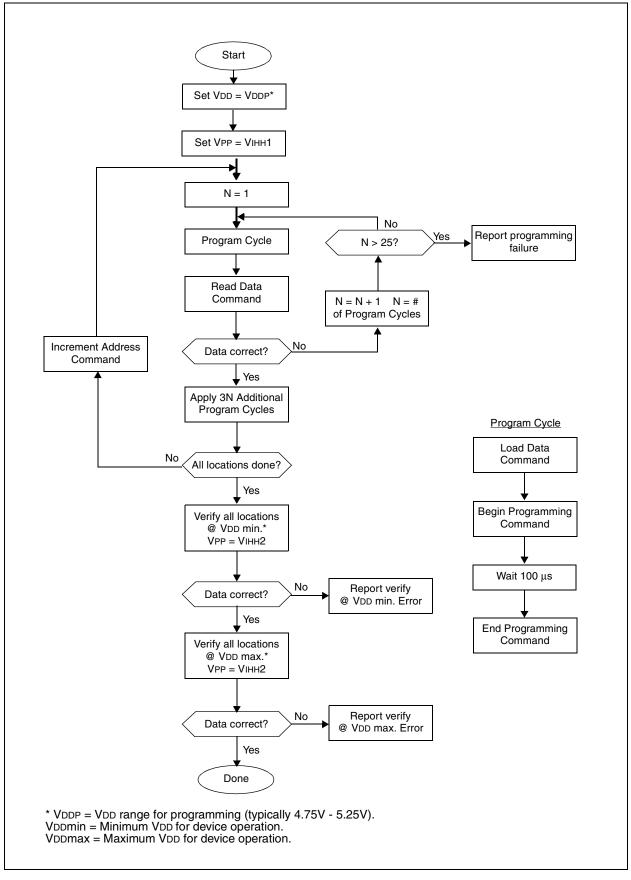

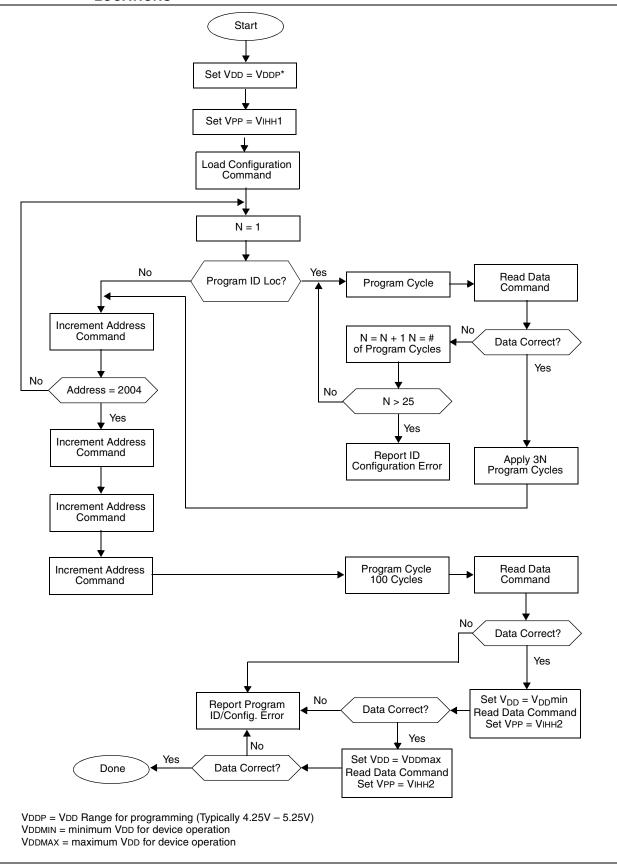

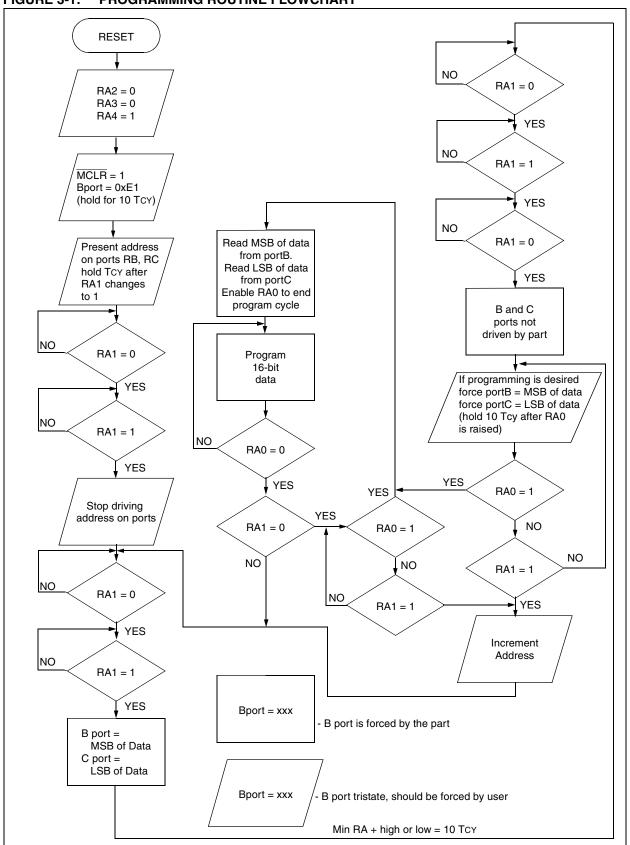

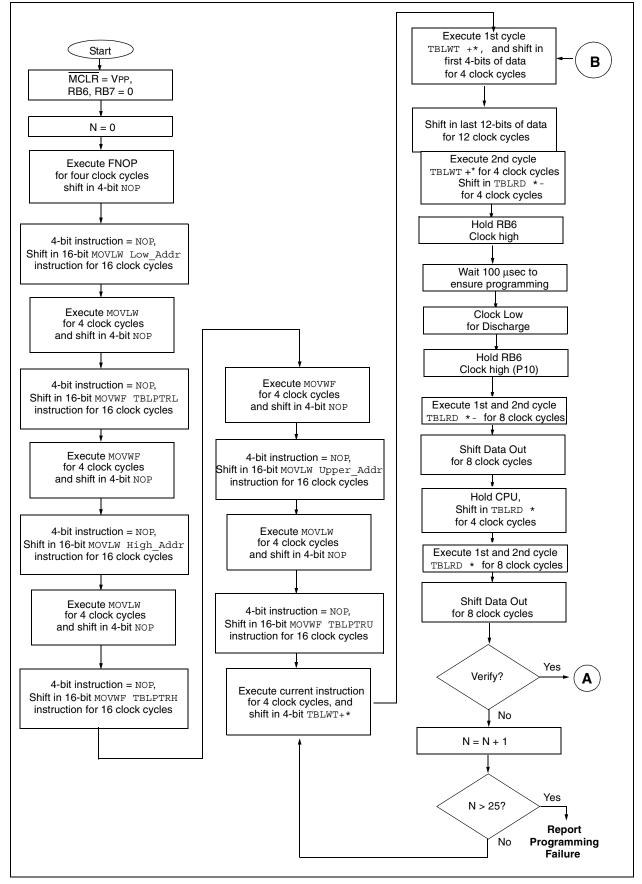

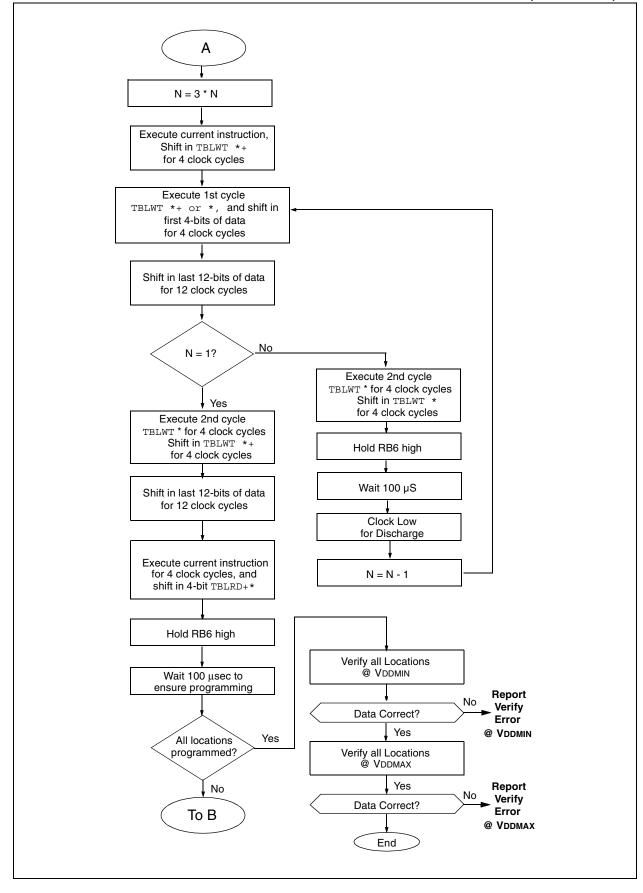

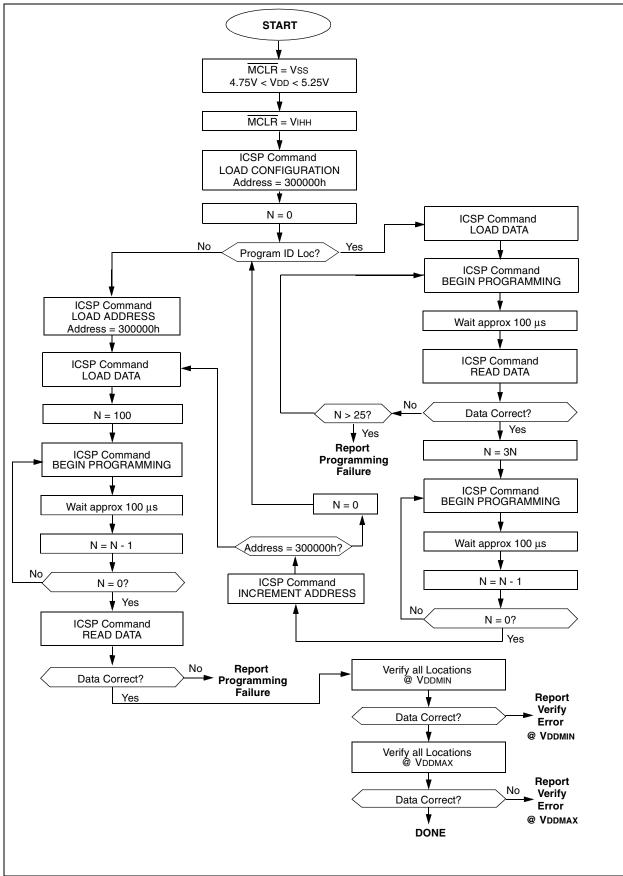

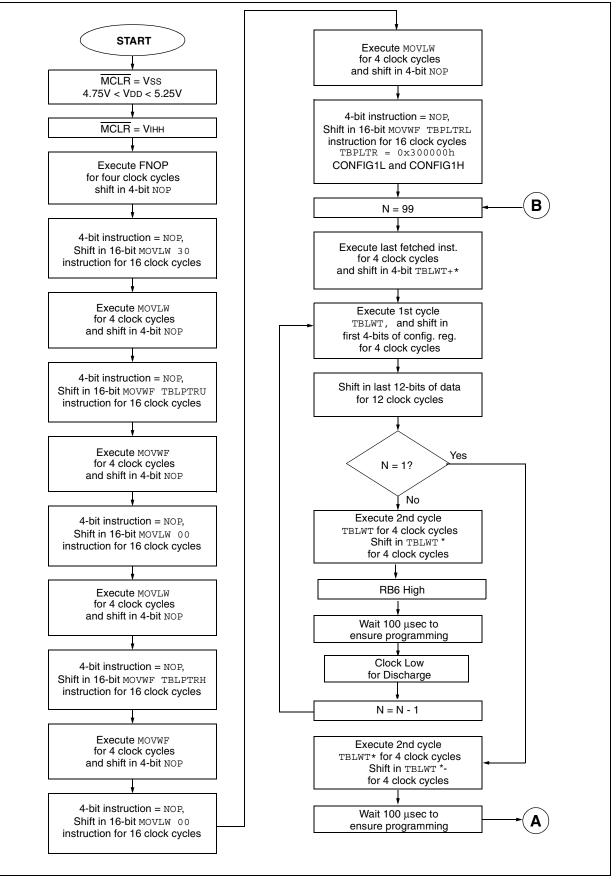

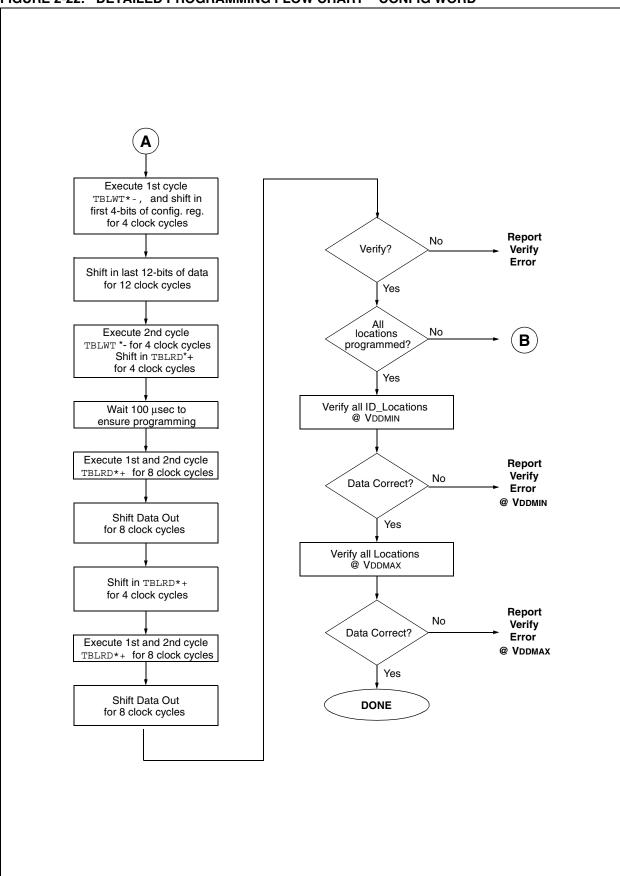

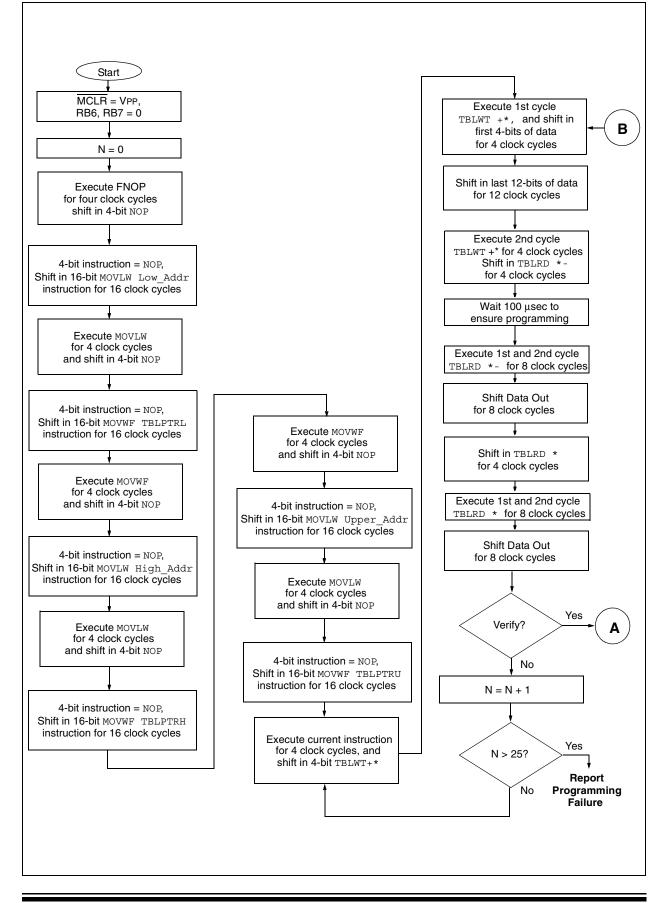

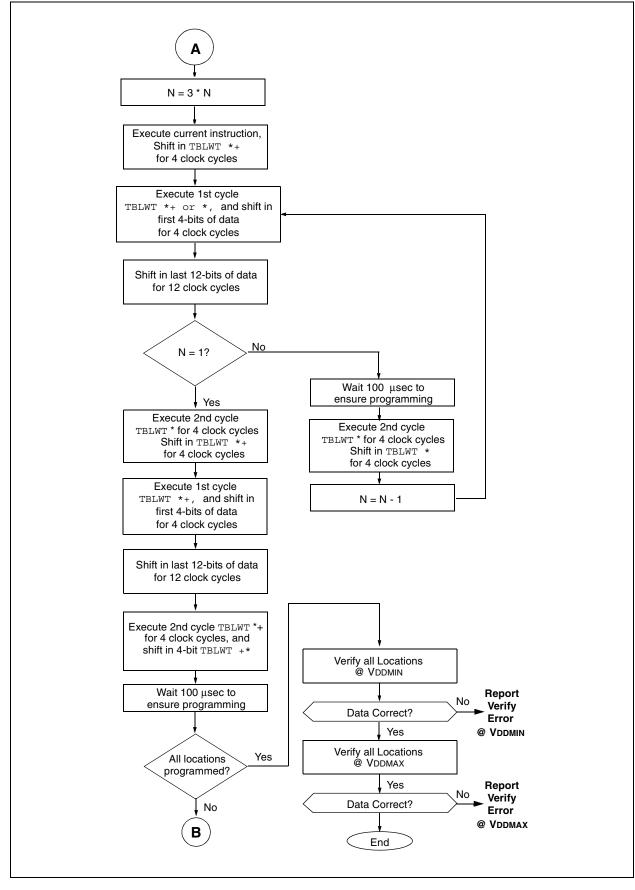

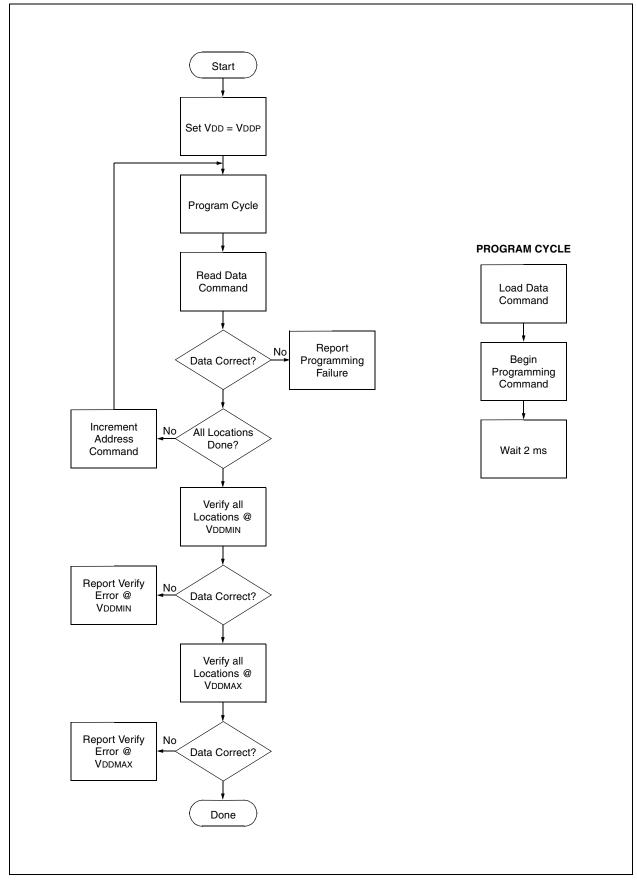

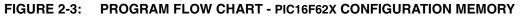

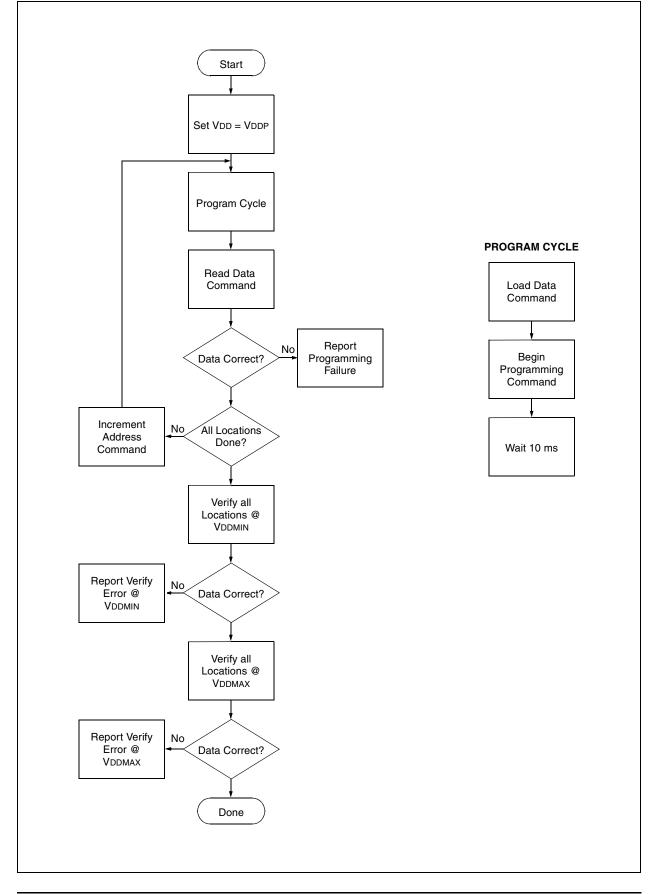

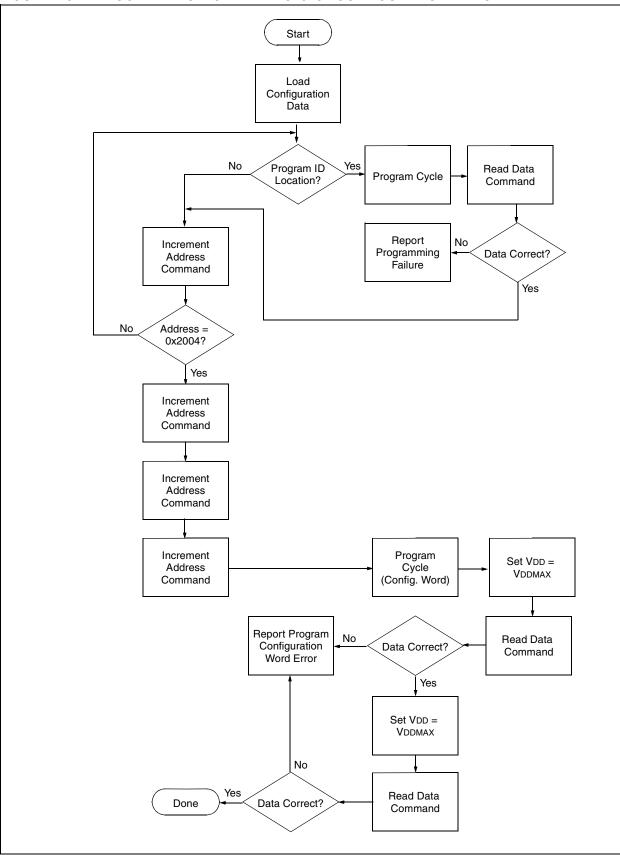

FIGURE 2-1: PROGRAMMING METHOD FLOWCHART

# PIC12C5XX

#### 2.3 Special Memory Locations

The highest address of program memory space is reserved for the internal RC oscillator calibration value. This location should not be overwritten except when this location is blank, and it should be verified, when programmed, that it is a MOVLW XX instruction.

The ID Locations area is only enabled if the device is in programming/verify mode. Thus, in normal operation mode only the memory location 0x000 to 0xNNN will be accessed and the Program Counter will just roll over from address 0xNNN to 0x000 when incremented.

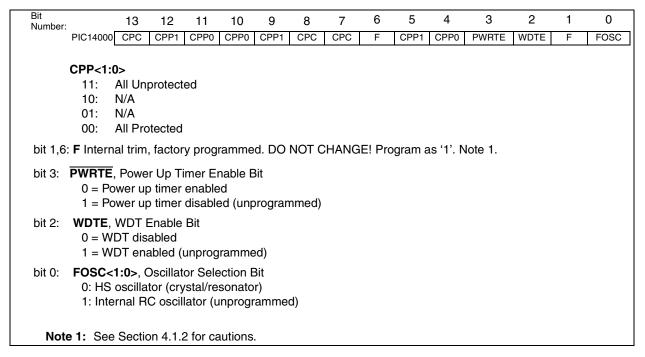

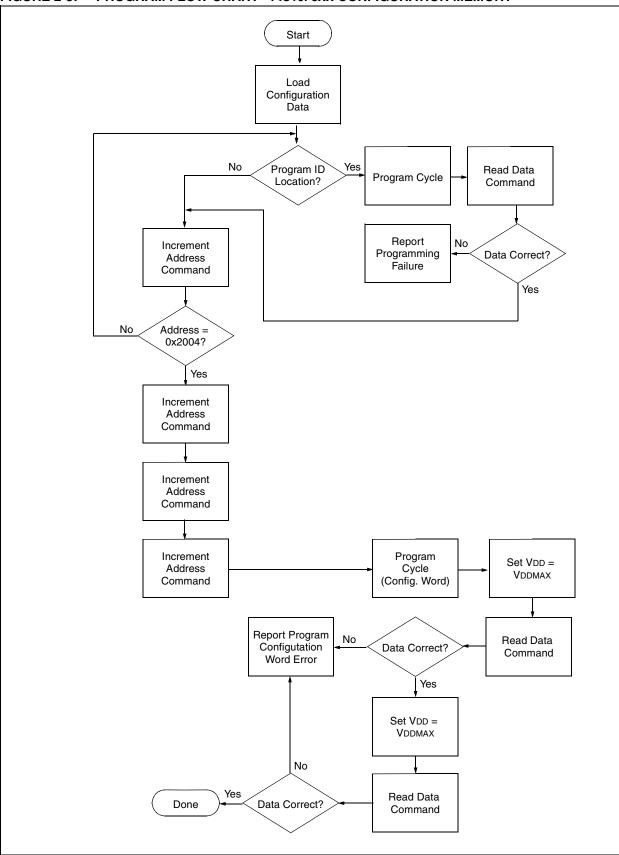

The configuration word can only be accessed immediately after MCLR going from VIL to VHH. The Program Counter will be set to all '1's upon MCLR = VIL. Thus, it has the value "0xFFF" when accessing the configuration EPROM. Incrementing the Program Counter once causes the Program Counter to roll over to all '0's. Incrementing the Program Counter 4K times after reset (MCLR = VIL) does not allow access to the configuration EPROM.

#### 2.3.1 CUSTOMER ID CODE LOCATIONS

Per definition, the first four words (address TTT to TTT + 3) are reserved for customer use. It is recommended that the customer use only the four lower order bits (bits 0 through 3) of each word and filling the eight higher order bits with '0's.

A user may want to store an identification code (ID) in the ID locations and still be able to read this code after the code protection bit was programmed.

#### EXAMPLE 2-1: CUSTOMER CODE 0xD1E2

The Customer ID code "0xD1E2" should be stored in the ID locations 0x200-0x203 like this (PIC12C508/ 508A/CE518):

| 200: | 0000 | 0000 | 1101 |

|------|------|------|------|

| 201: | 0000 | 0000 | 0001 |

| 202: | 0000 | 0000 | 1110 |

| 203: | 0000 | 0000 | 0010 |

Reading these four memory locations, even with the code protection bit programmed would still output on GP0 the bit sequence "1101", "0001", "1110", "0010" which is "0xD1E2".

| Note: | All other locations in PICmicro <sup>®</sup> MCU con- |                  |  |  |

|-------|-------------------------------------------------------|------------------|--|--|

|       | figuration memory a                                   | are reserved and |  |  |

|       | should not be programmed.                             |                  |  |  |

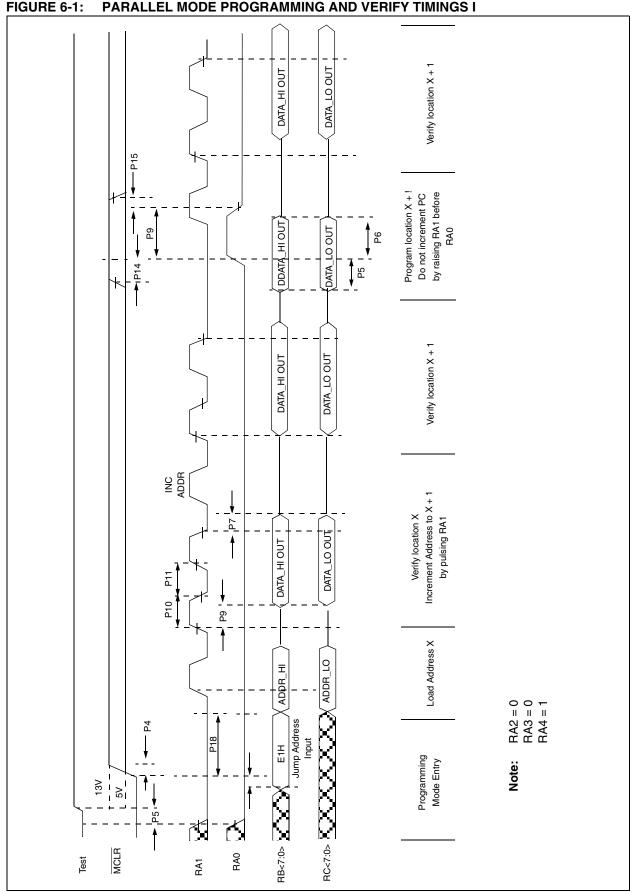

#### 2.4 Program/Verify Mode

The program/verify mode is entered by holding pins GP1 and GP0 low while raising MCLR pin from VIL to VIHH (high voltage). Once in this mode the user program memory and the configuration memory can be accessed and programmed in serial fashion. The mode of operation is serial. GP0 and GP1 are Schmitt Trigger inputs in this mode.

The sequence that enters the device into the programming/verify mode places all other logic into the reset state (the MCLR pin was initially at VIL). This means that all I/O are in the reset state (High impedance inputs).

Note: The MCLR pin should be raised from VIL to VIHH within 9 ms of VDD rise. This is to ensure that the device does not have the PC incremented while in valid operation range.

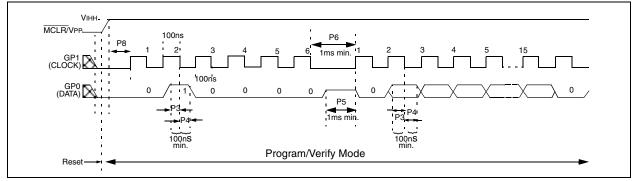

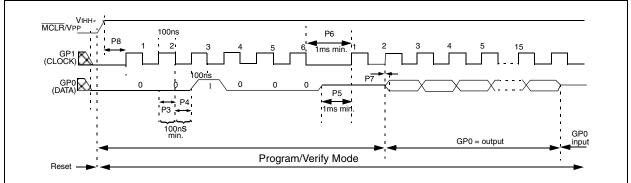

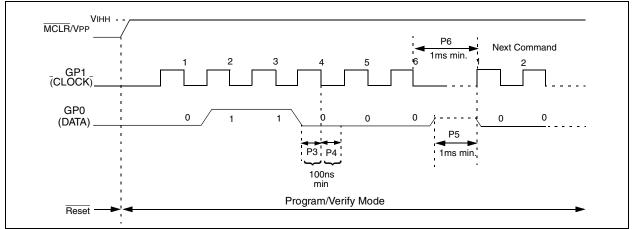

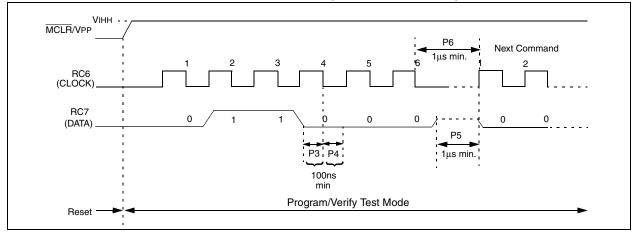

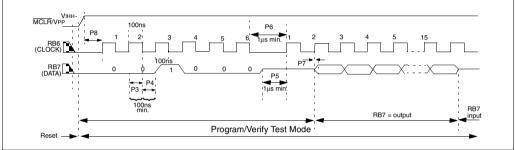

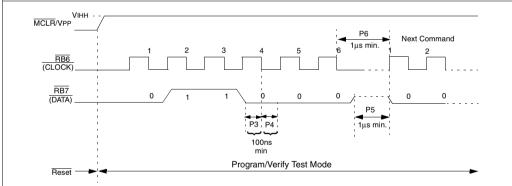

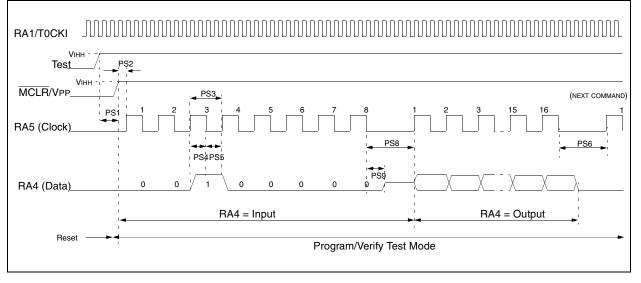

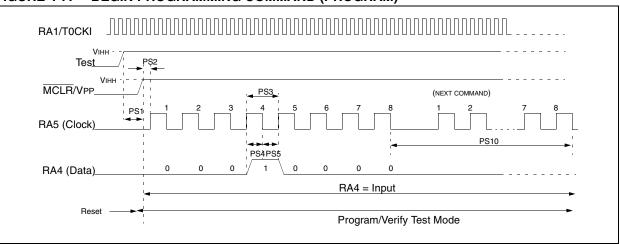

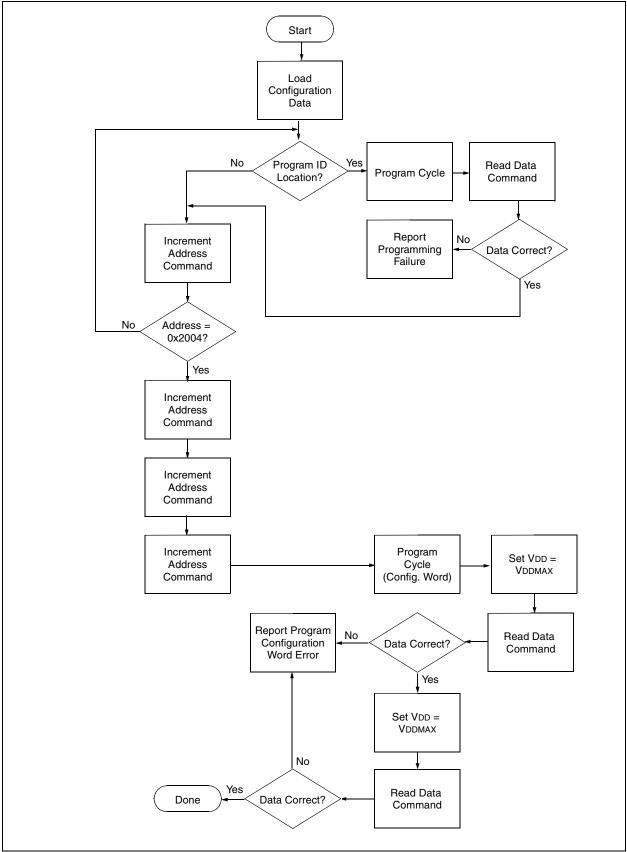

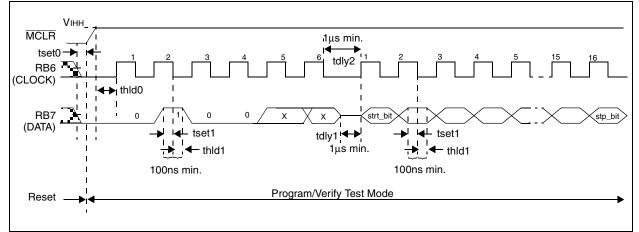

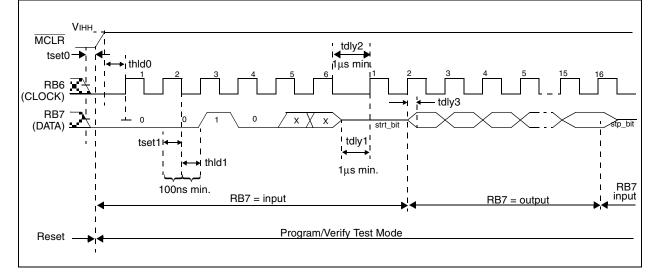

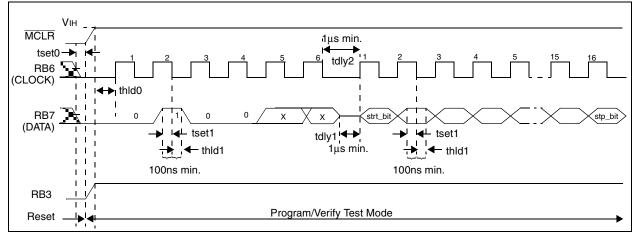

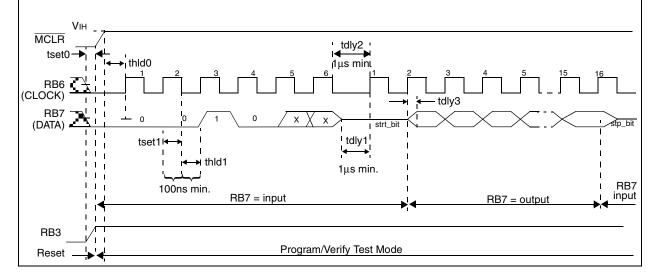

#### 2.4.1 PROGRAM/VERIFY OPERATION

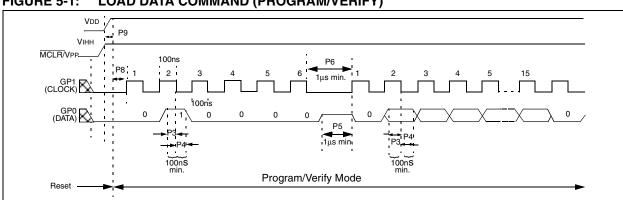

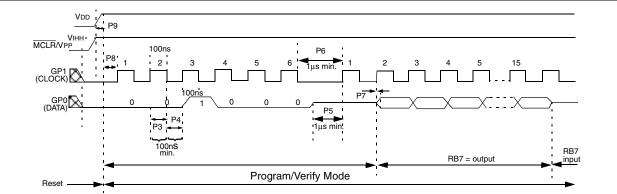

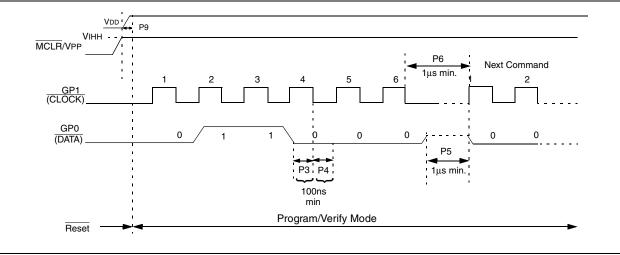

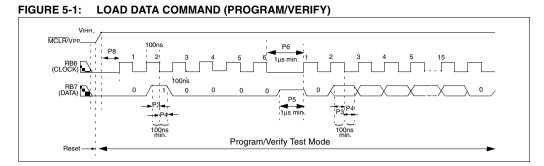

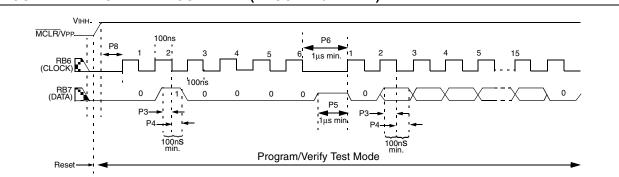

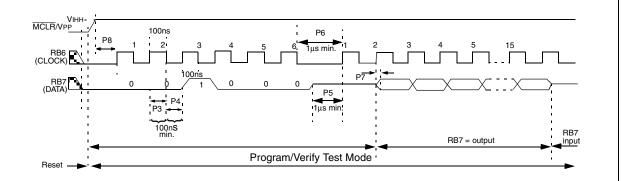

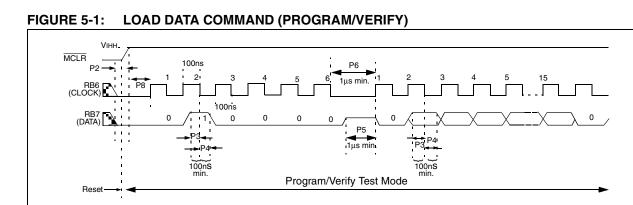

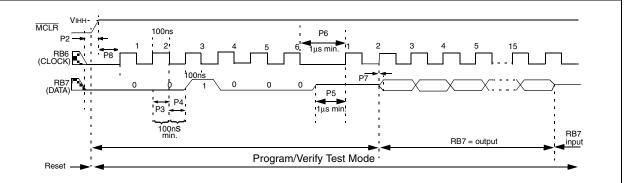

The GP1 pin is used as a clock input pin, and the GP0 pin is used for entering command bits and data input/ output during serial operation. To input a command, the clock pin (GP1) is cycled six times. Each command bit is latched on the falling edge of the clock with the least significant bit (LSB) of the command being input first. The data on pin GP0 is required to have a minimum setup and hold time (see AC/DC specs) with respect to the falling edge of the clock. Commands that have data associated with them (read and load) are specified to have a minimum delay of 1  $\mu$ s between the command and the data. After this delay the clock pin is cycled 16 times with the first cycle being a start bit and the last cycle being a stop bit. Data is also input and output LSB first. Therefore, during a read operation the LSB will be transmitted onto pin GP0 on the rising edge of the second cycle, and during a load operation the LSB will be latched on the falling edge of the second cycle. A minimum 1 µs delay is also specified between consecutive commands.

All commands are transmitted LSB first. Data words are also transmitted LSB first. The data is transmitted on the rising edge and latched on the falling edge of the clock. To allow for decoding of commands and reversal of data pin configuration, a time separation of at least 1  $\mu$ s is required between a command and a data word (or another command).

The commands that are available are listed in Table .

| Command           |   | Ма | pping | (MSB | LSE | 3) | Data           |

|-------------------|---|----|-------|------|-----|----|----------------|

| Load Data         | 0 | 0  | 0     | 0    | 1   | 0  | 0, data(14), 0 |

| Read Data         | 0 | 0  | 0     | 1    | 0   | 0  | 0, data(14), 0 |

| Increment Address | 0 | 0  | 0     | 1    | 1   | 0  |                |

| Begin programming | 0 | 0  | 1     | 0    | 0   | 0  |                |

| End Programming   | 0 | 0  | 1     | 1    | 1   | 0  |                |

Note: The clock must be disabled during in-circuit programming.

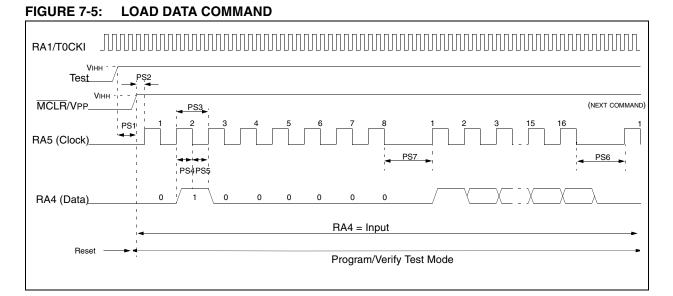

#### 2.4.1.1 LOAD DATA

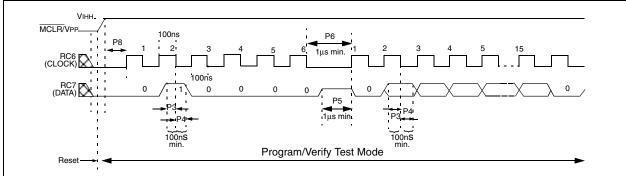

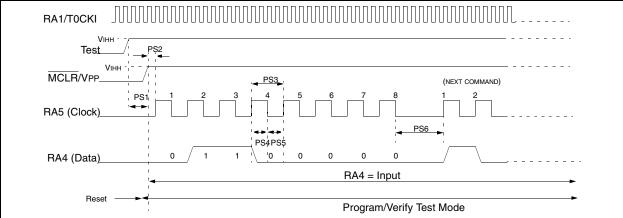

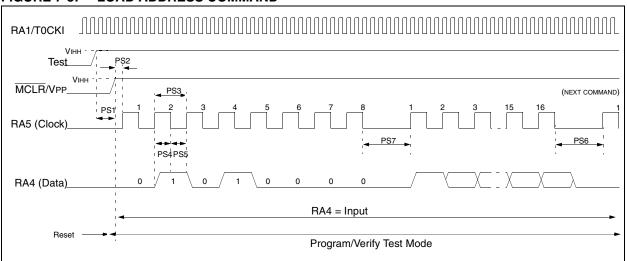

After receiving this command, the chip will load in a 14-bit "data word" when 16 cycles are applied, as described previously. Because this is a 12 bit core, the two msb's of the data word are ignored. A timing diagram for the load data command is shown in Figure 5-1.

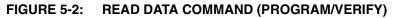

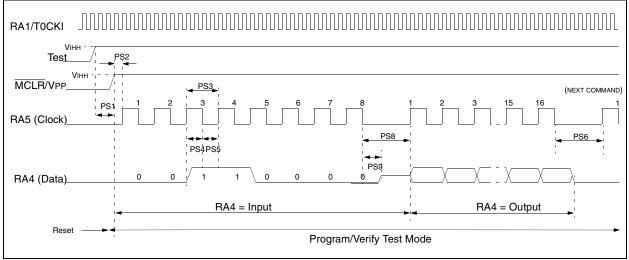

#### 2.4.1.2 READ DATA

After receiving this command, the chip will transmit data bits out of the memory currently accessed starting with the second rising edge of the clock input. The GP0 pin will go into output mode on the second rising clock edge, and it will revert back to input mode (hi-impedance) after the 16th rising edge. Because this is a 12-bit core, the two MSB's of the data are unused and read as '0'. A timing diagram of this command is shown in Figure 5-2.

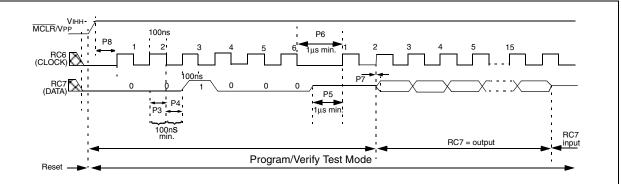

#### 2.4.1.3 INCREMENT ADDRESS

The PC is incremented when this command is received. A timing diagram of this command is shown in Figure 5-3.

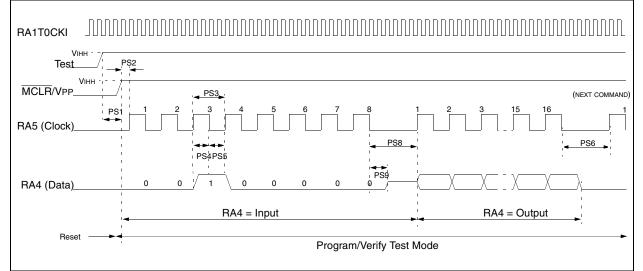

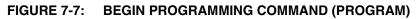

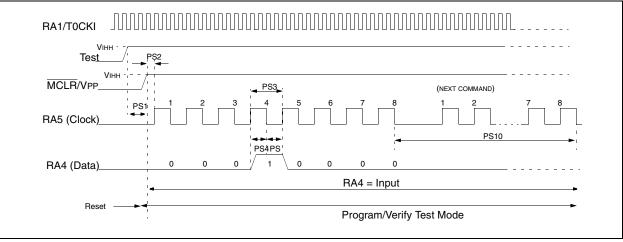

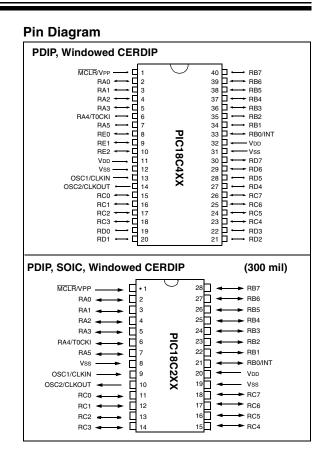

#### 2.4.1.4 BEGIN PROGRAMMING